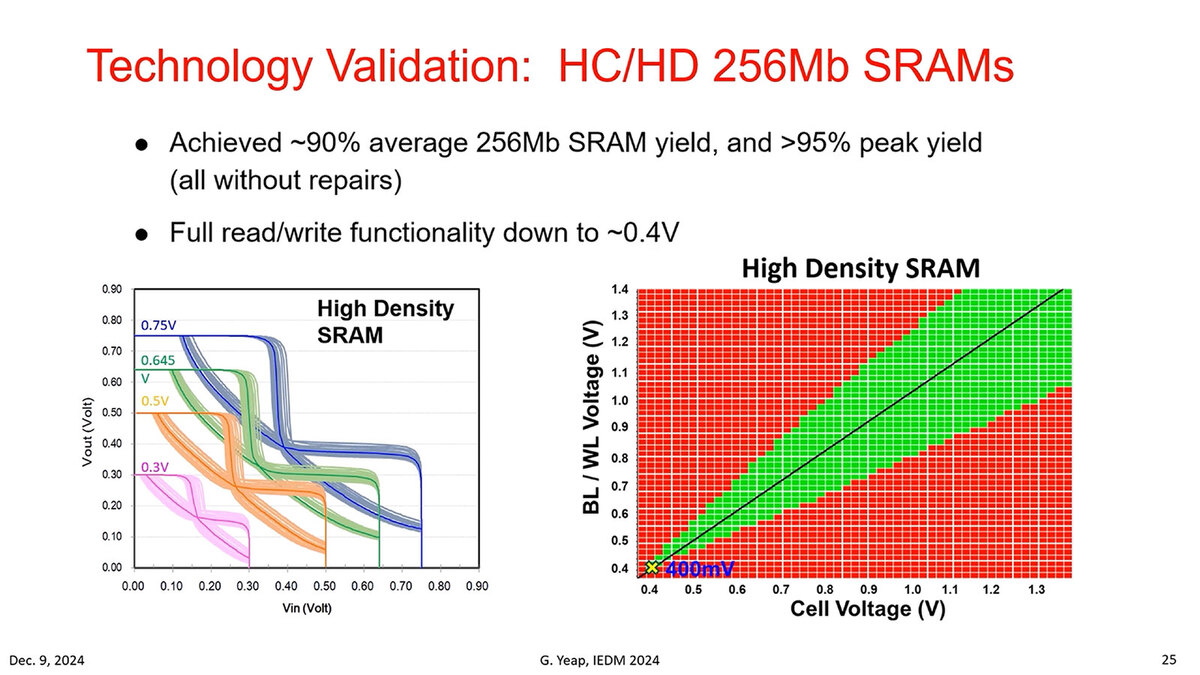

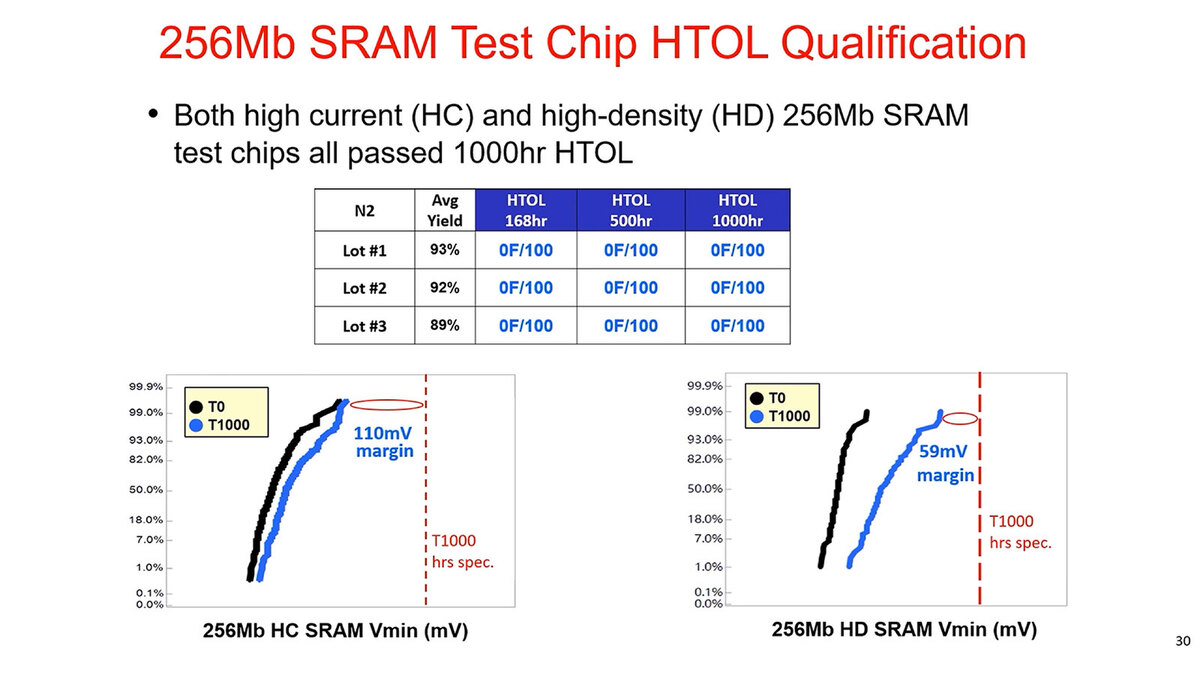

SRAMの歩留まりは平均90%、最大95%以上

おもしろいデータがある。HC/HD両方におけるSRAMを製造してその特性を確認したのだが、この際に歩留まりが平均90%、最大95%以上という数字が示されている。

もう少し具体的なデータが下の画像で、高温動作寿命試験で1000時間を過ぎても不良が1つも出なかった、としている。

HTOLはHigh Temperature Operating Lifeの意味で、高温動作寿命試験のこと。正確な数字は不明だが、通常では動作限界(例えば125度)で1000時間の連続稼働などをさせるわけだ

それはともかくとして、2ページ前の最後の画像にあるとおりN2は38.1Mbit/mm2という密度だとされたので、この256MbitのテストチップのSRAMの面積は6.8mm2ほどでしかないことになる。正方形だとすると1辺2.6mmほどだ。ただこれは純粋にSRAMだけの面積だが、動作試験をするためにはこのSRAMに読み書きをさせるための回路が必要だし、外部のテスターと接続するための端子部も必要になる。

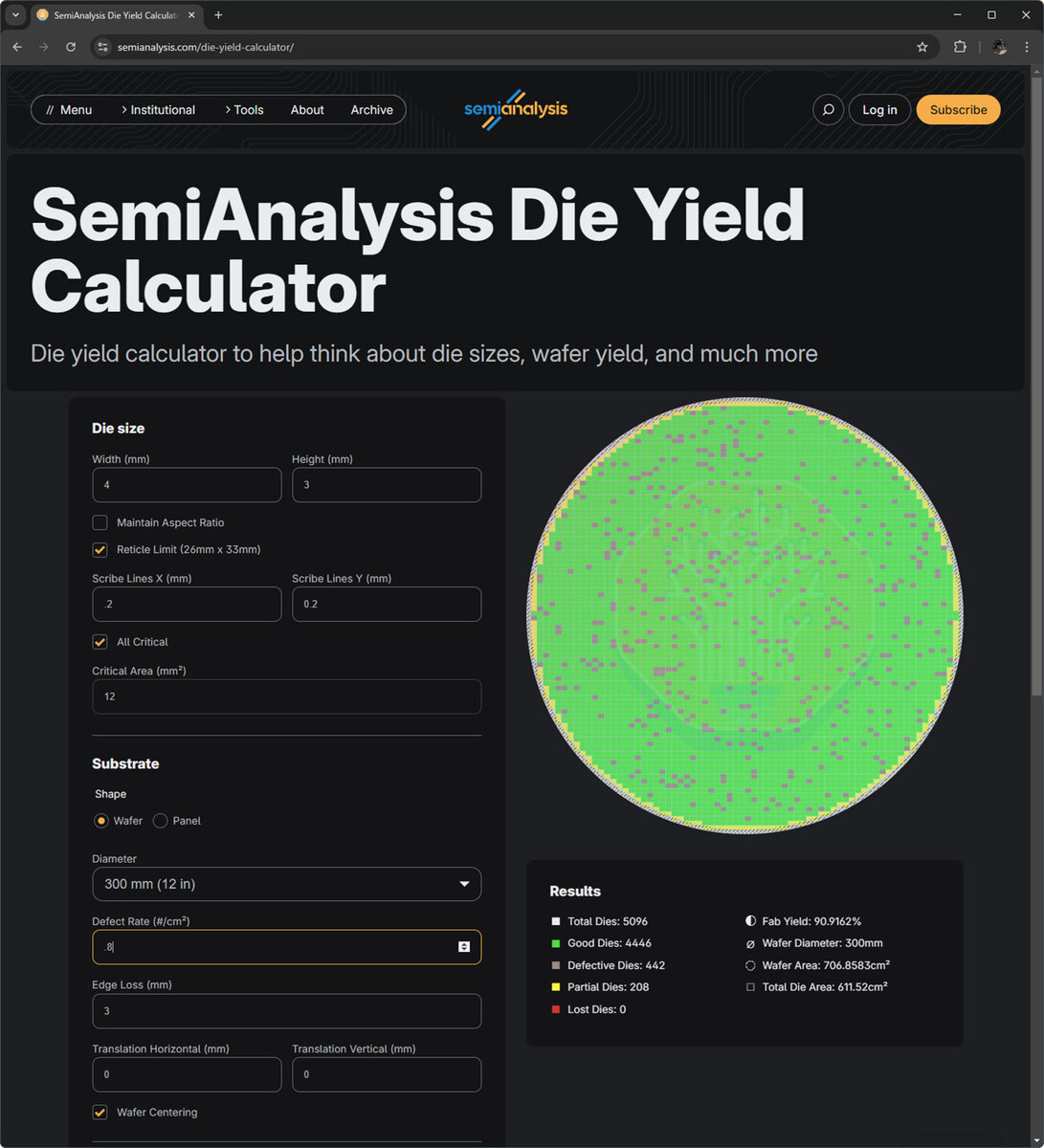

仮にこのあたりも加味して4×3mmと仮定して、SemiAnalysisのDie Yield Calculatorで試算してみると、欠陥密度は0.8個/cm2ほどになる。昨年9月にインテルがIntel 18Aの現状を紹介した時の欠陥密度は0.4個/cm2だったから、これの倍くらいということか?

ダイサイズと欠陥密度(Defect Density)を入れると、歩留まり(Yield)を計算してくれる。逆に歩留まりがわかっていれば、その数値に近づくように欠陥密度を調整することで、大まかな欠陥密度が推定できる

もっともこれは4×3mmという小さいダイだと仮定した場合の話である。Intel 18AベースのSRAMテスト用ウェハーの場合、ダイの大きさはおおむね8.9×5.9mmと一回り大きい。もしこれと同じ大きさだとすれば、欠陥密度は0.2個cm2とはるかに優れた数値になる。

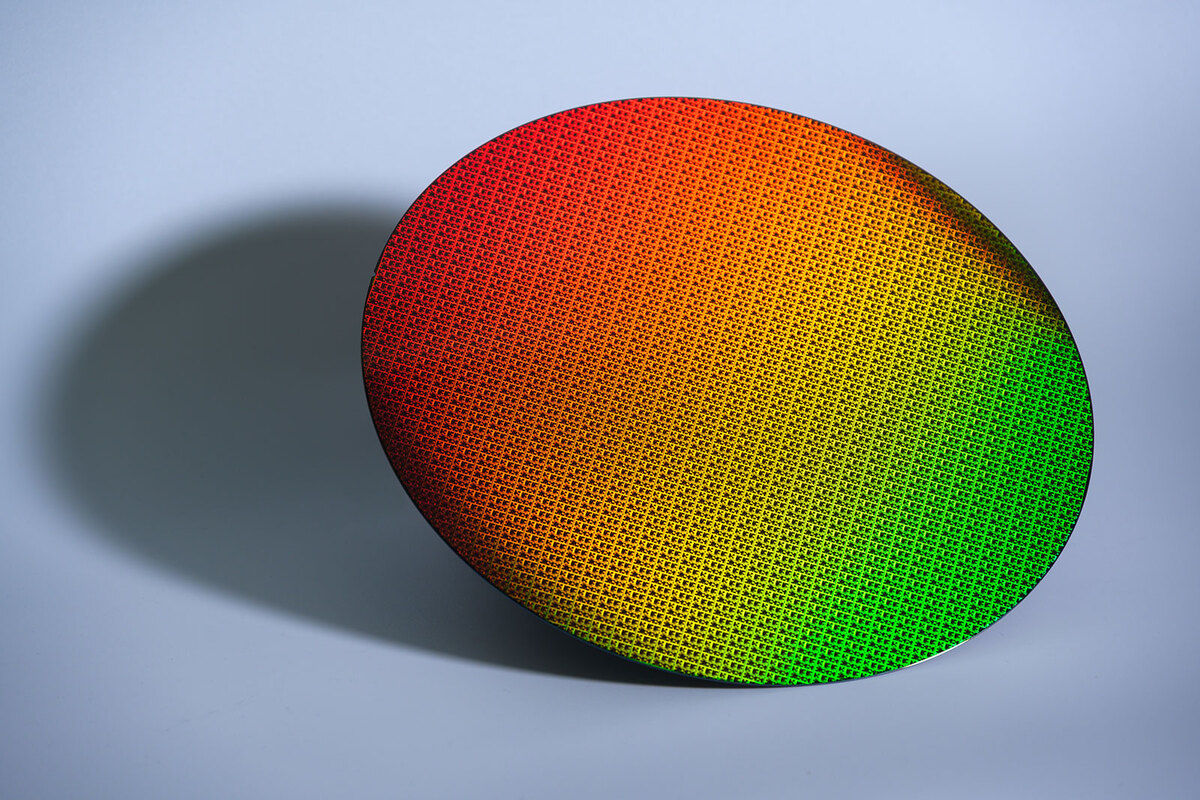

余談になるがIntel 18Aが0.4個/cm2未満とされており、なので2つ上の画像にあるウェハーにおけるSRAMテストチップの歩留まりは81%強と考えられる。このあたりはTSMCのウェハーが公開されればわかるのだが、あえてそのあたりを計算されたくなくてウェハーを示していないのだろう、とは想像がつく。

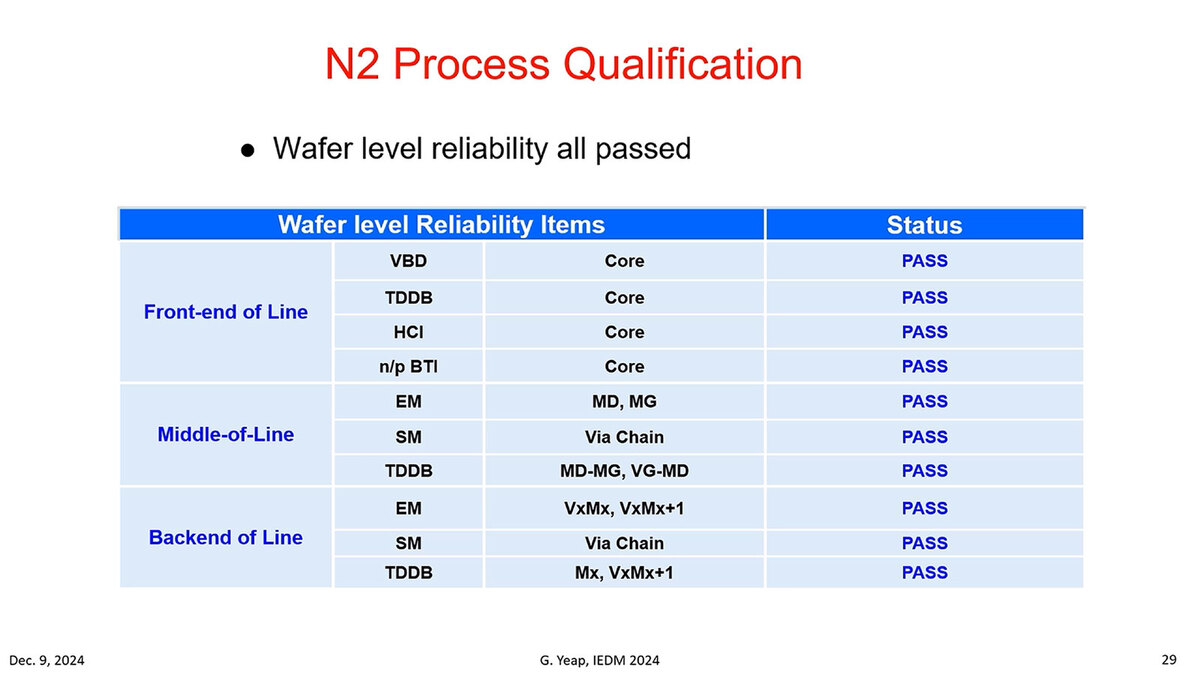

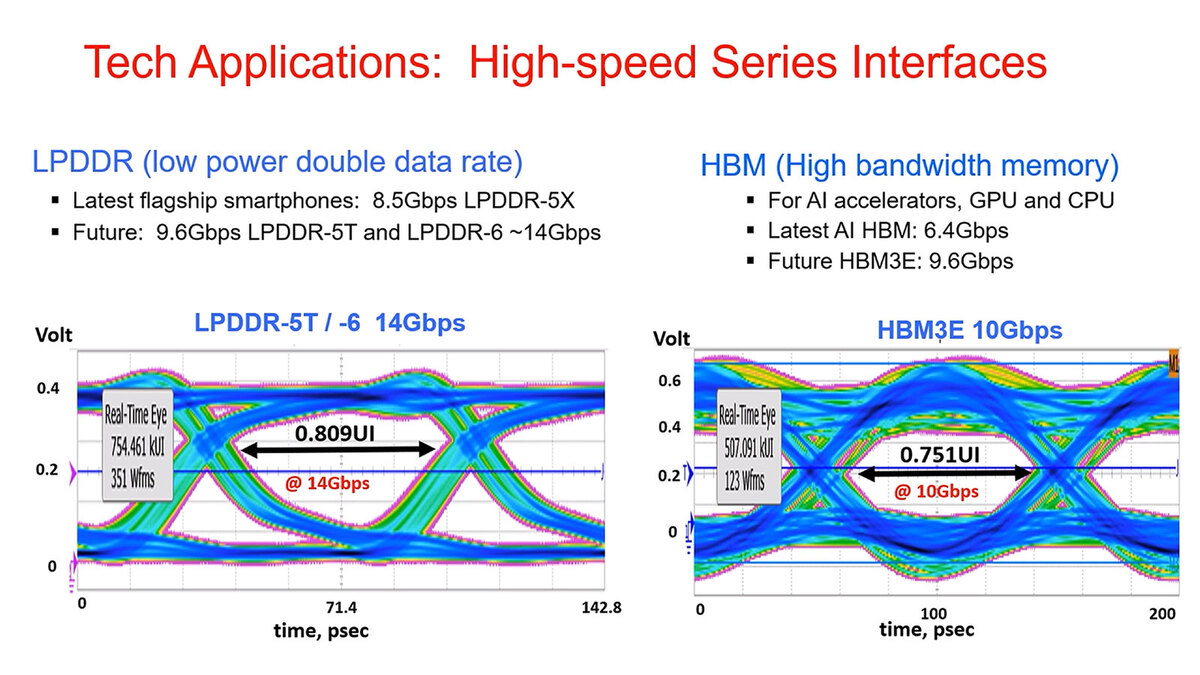

ちなみにその他の話として、LPDDR5/6やHBM3eとの接続も問題なく実装できていることが、これも実測データで示された。各種信頼性試験に関してもすでにすべてウェハーレベルでパスしているとしている。

昨今はメモリーコントローラーはもう少し古めのプロセスを使ったチップレットにするのが一般的ではあるが、逆に言えばチップレット接続用のPHYを構成する際も、少なくとも14Gbpsくらいまでは問題なく構成できることが示されたともいえる

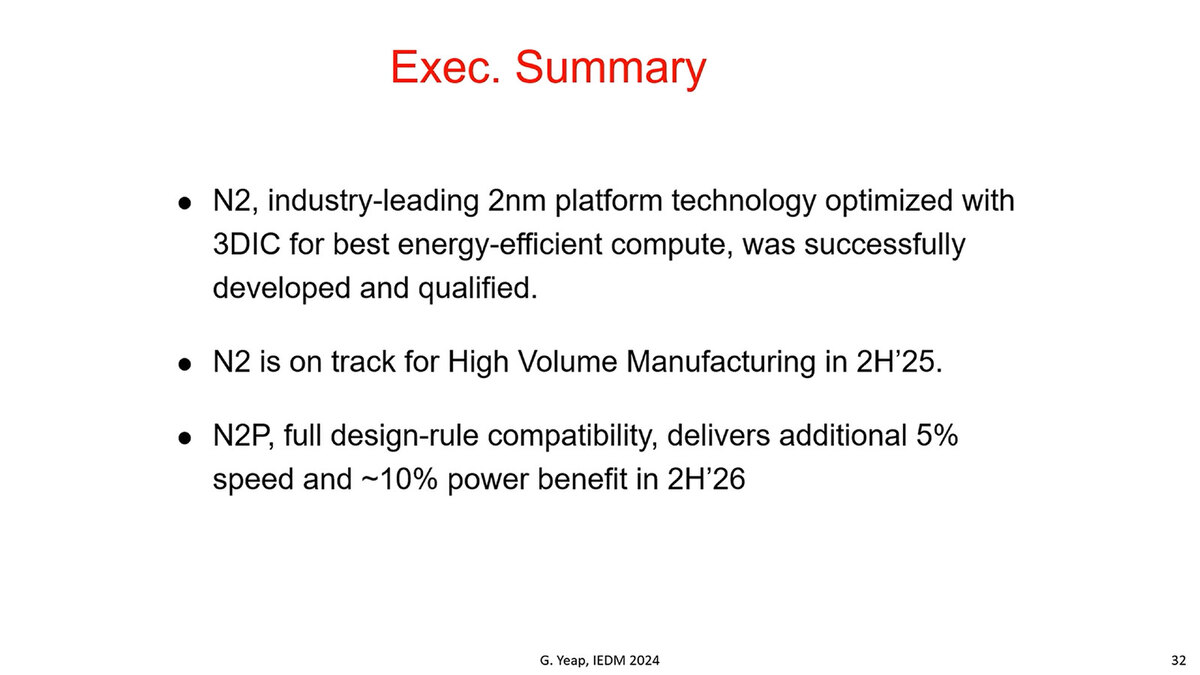

今のところTSMCは2025年後半の量産開始のスケジュールに変更はないとしており、性能向上型のN2Pも2026年後半に量産開始となる、という予定に変更はないとする。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります