フィンの数ではなくナノシートの数を増減させる技術

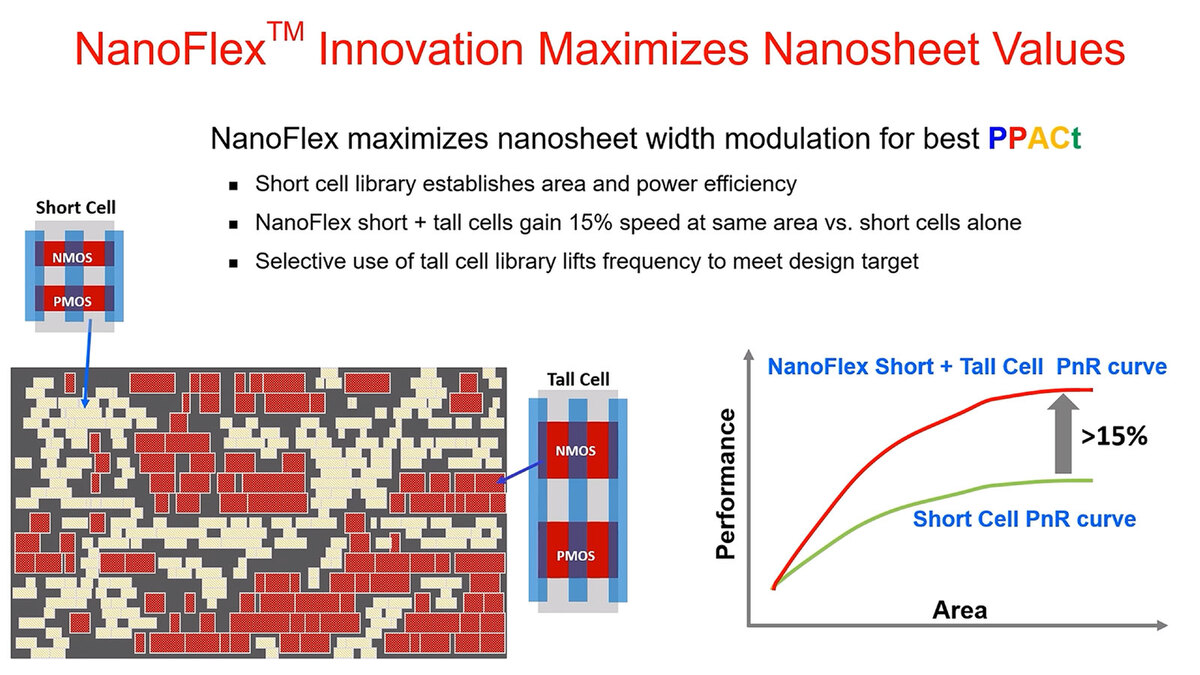

NanoFlex

最適化の一助となるのが、NanoFlexと呼ばれる技術である。もともとTSMCはN3の時点でFinFlexと呼ばれる、特性を変えた3種類のトランジスタを用意、これを組み合わせることで望む特性を簡単に得やすくする技術を提供していた。

NanoFlexの概要。Short Cellはシートの数が少なく、高密度/省電力型、一方Tall Cellはシートの数が大きく、高速型となる。実際にはShortとTallだけでなく、複数の選択肢があると思われる

実際には複数のフィン数の組み合わせ(NMOS/PMOSでそれぞれ3/2枚、2/2枚、2/1枚となる構成)をあらかじめ用意し、これを利用して簡単に回路を構築できるようにするというものだが、NanoFlexはフィンの数ではなくナノシートの数を増減させて同じことが可能になるようにしている。

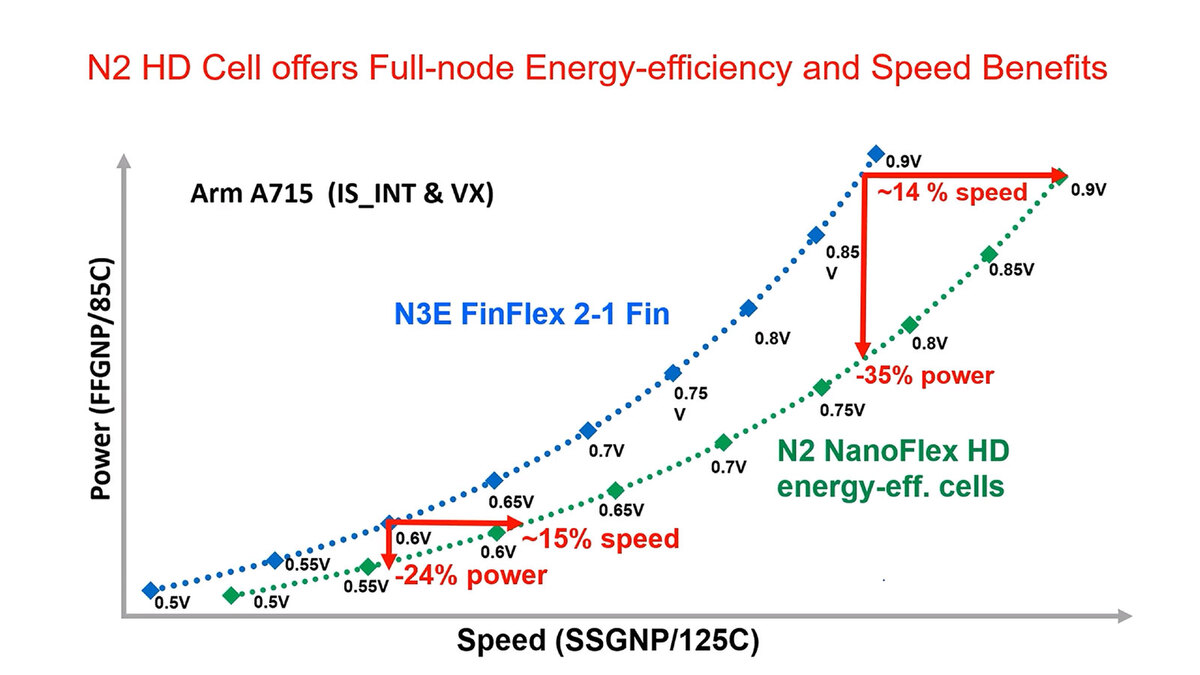

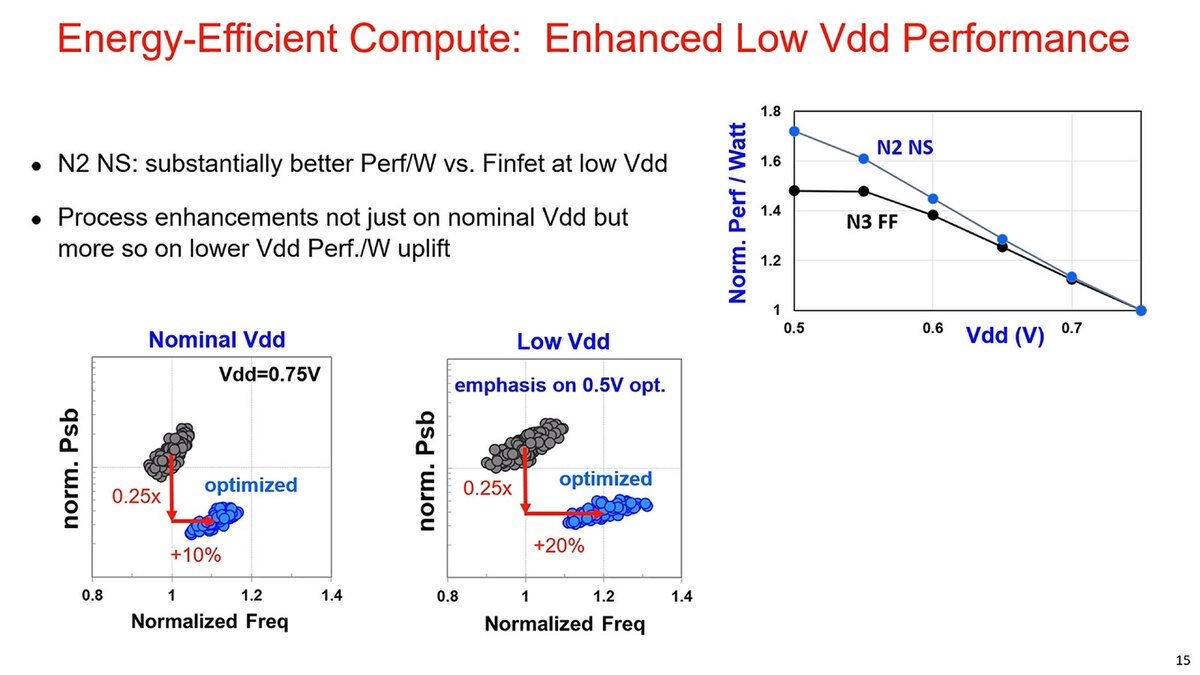

実際にN3EおよびN2プロセスを利用し、Cortex-A715コアを稼働させたときの性能/消費電力の比較も示された。下の画像は省電力同士、つまりN3Eなら2-1構成のもので、一方N2はShort Cellを利用したNanoFlex HDを利用したもので、ピークでは14%高速ないし35%の省電力、0.6V付近では15%高速ないし24%の省電力化が実現できたとする。

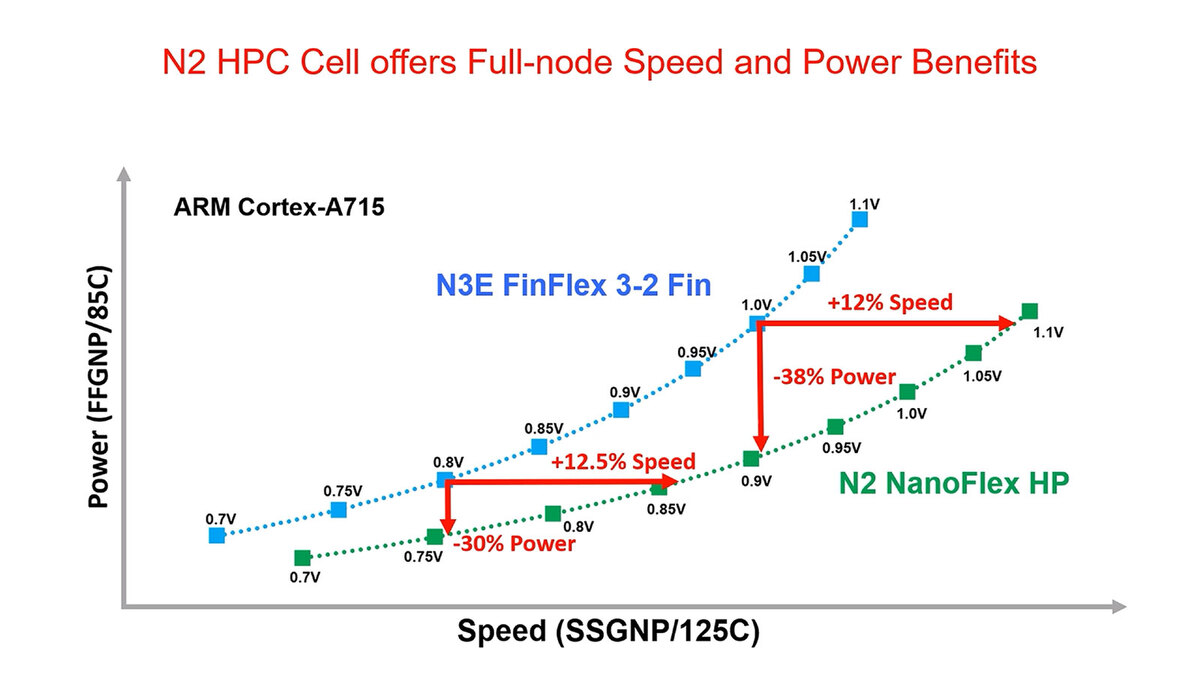

一方高速同士、つまりN3EがFinFlex 3-2、N2がTall Cellを使ったNanoFlex HPの場合の比較が下の画像だ。動作周波数の向上は12%ないし12.5%とやや小さめだが、その代わり38%ないし30%と省電力同士の場合よりも電力削減効果が大きいものとなっているとする。

ちなみにNanoFlexはHD Short Cell/HD cell/HPC cellの大きく3種類に向けたソリューションとなっている。

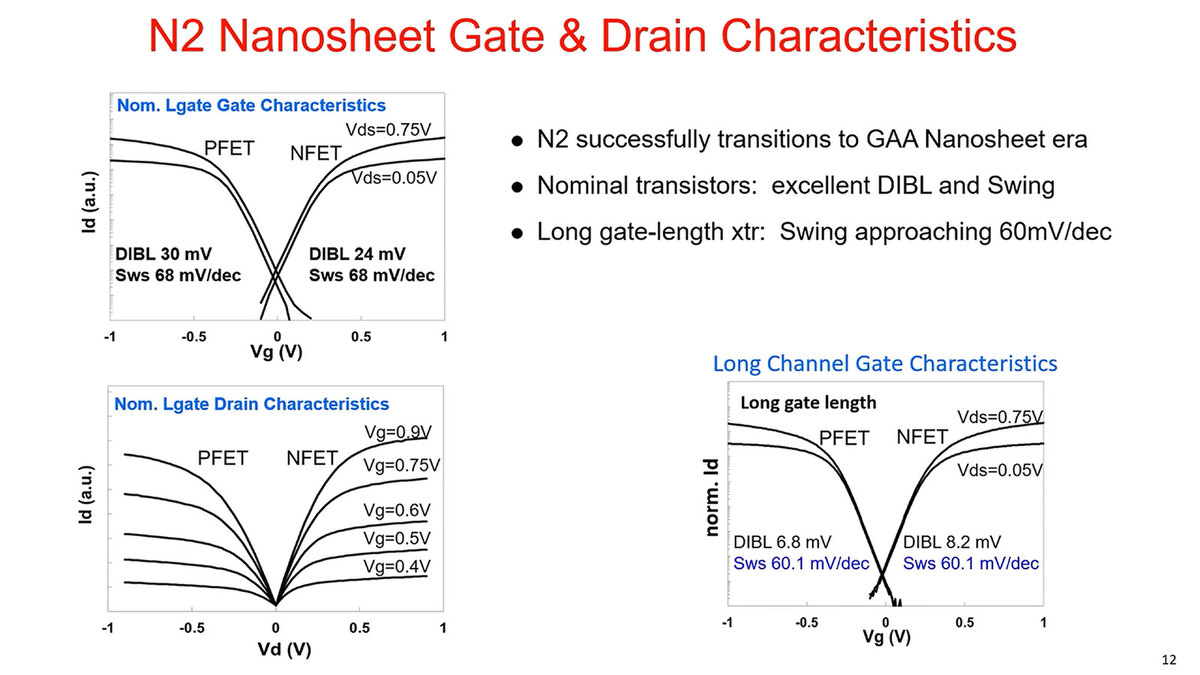

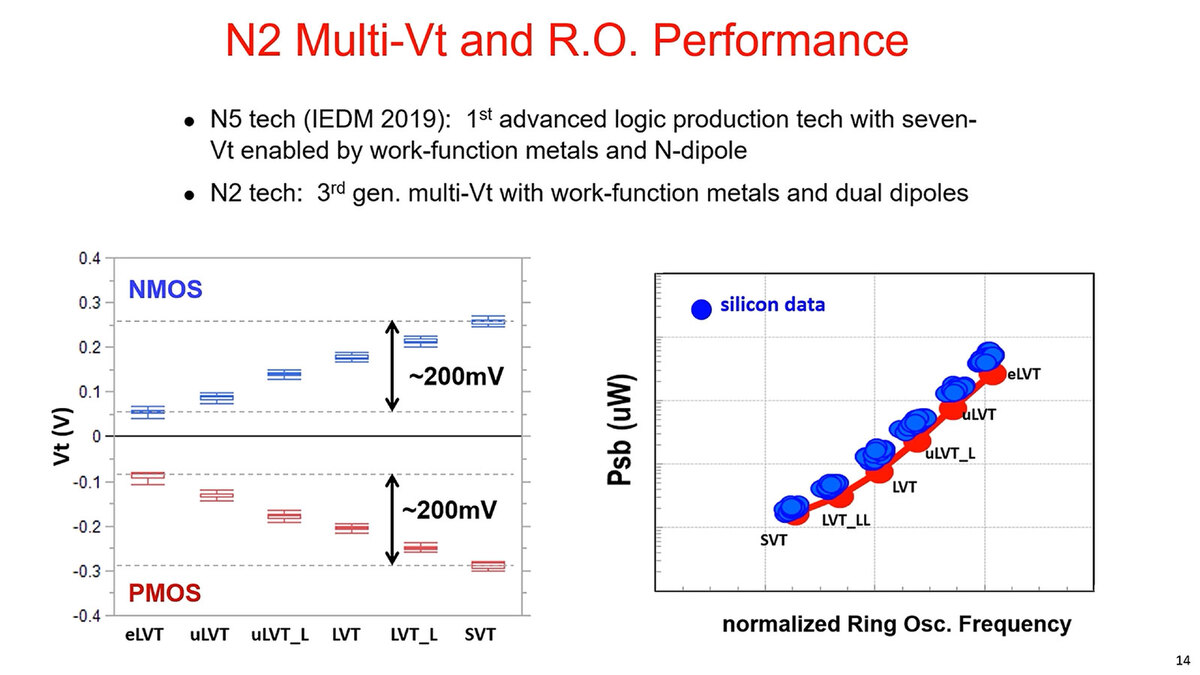

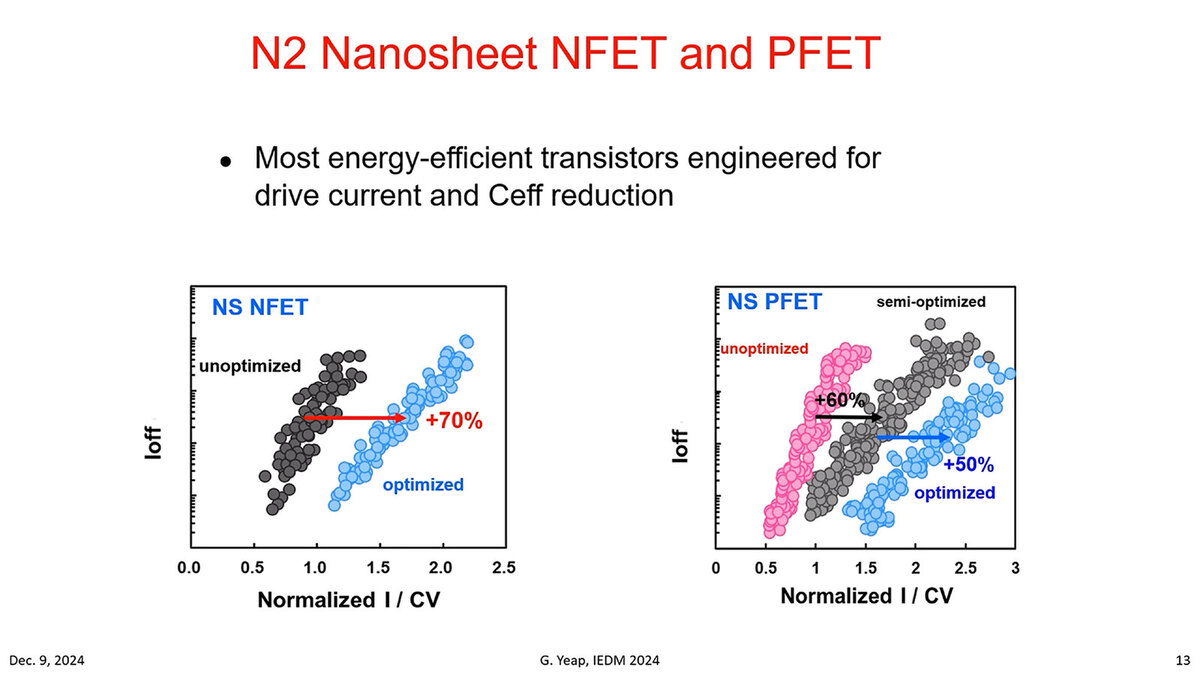

そのN2世代のトランジスタの基本的な特性が下にある4つの画像となる。細かくは説明しないが、既存のN3Eと比較しても十分性能改善がなされていることが、実際のシリコンでのデータを元に示されたことは大きい。

Ioff(トランジスタオフ時のリーク電流)の比較。縦軸がリーク電流、横軸がレイテンシーの逆数である。傾向としてはグラフが右にずれればずれるほど、リークが少ないことになる。PMOSのSemi-optimizedというのがどういう状況なのが気になるところ

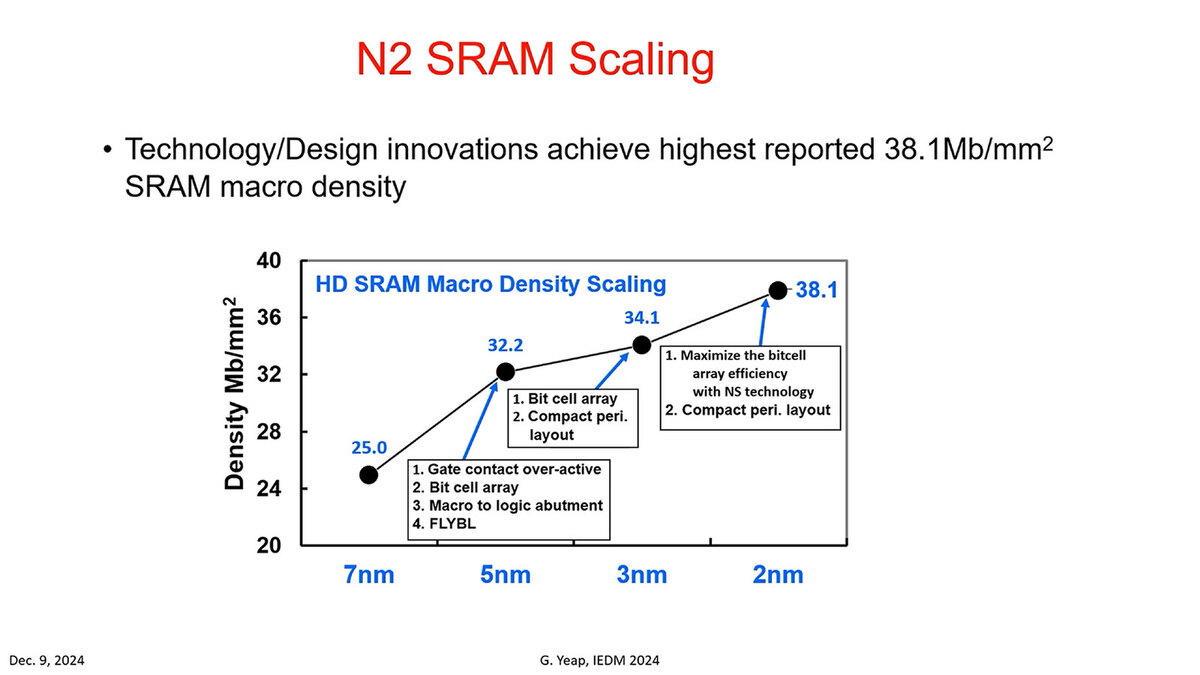

興味深いのSRAMである。何度か書いたが、トランジスタの微細化が進んでもSRAMの密度が上がらない、というのが目下の問題である。これはトランジスタそのものの大きさより配線の方がむしろ阻害要因になっているからだが、それでも2nmでは38.1Mbit/mm2まで密度を上げられたとしている。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります