第808回

酸化ハフニウム(HfO2)でフィンをカバーすると性能が改善、TMD半導体の実現に近づく IEDM 2024レポート

2025年01月27日 12時00分更新

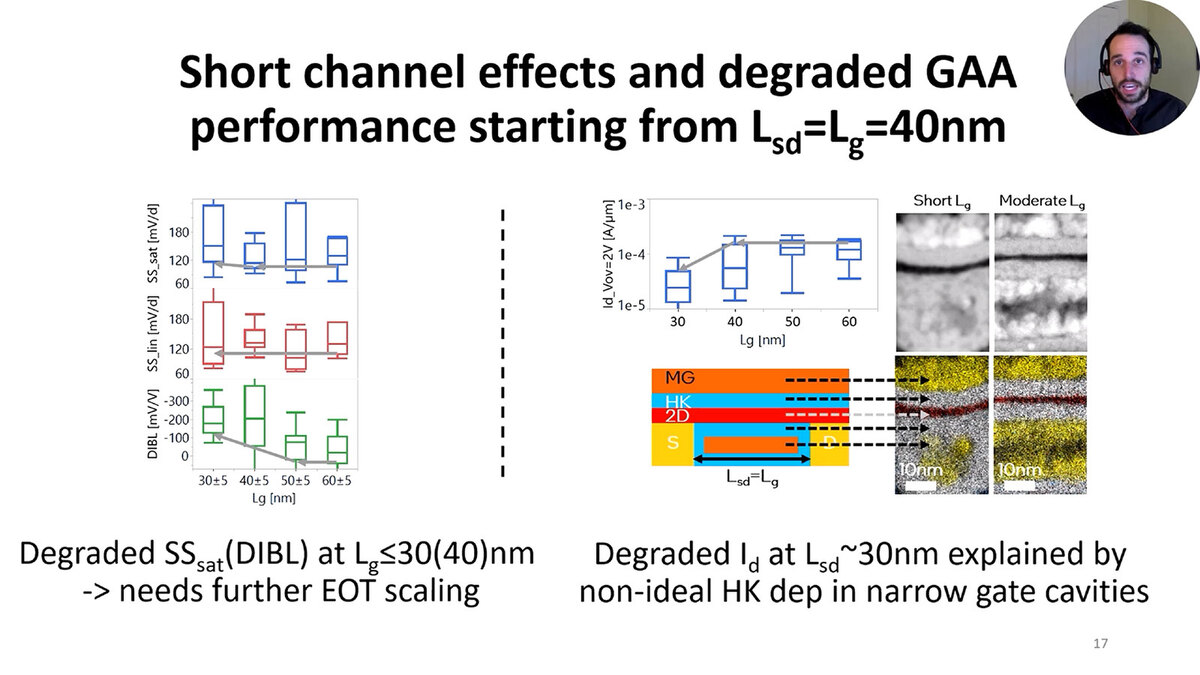

ゲート長を60nmから30nmまで短縮すると性能が出ない

次にこの状態でゲート長を60nmから30nmまで短縮した場合の特性を調べたのが下の画像である。

左側のグラフで、SSsatなどはそれほど大きな違いはないが、DIBLがLg=60nmの時は17mV/Vと低い値なのが、30nmまで短縮すると177mV/Vまで増加しているのがわかる。これはさらなるEOT(Equivalent Oxide Thickness:等価酸化膜厚)スケーリングが必要、というのがここでの結論である。

右側は2Vでのオーバードライブ駆動時の駆動電流を比較したもので、Lgを30nmにすると顕著に電流が劣化する。これはチャネルの形状が劣化することで、不十分な構成のGAAが形成されてしまい、GAAの利点が失われてしまうためで、これに関してさらなる最適化が必要、としている。

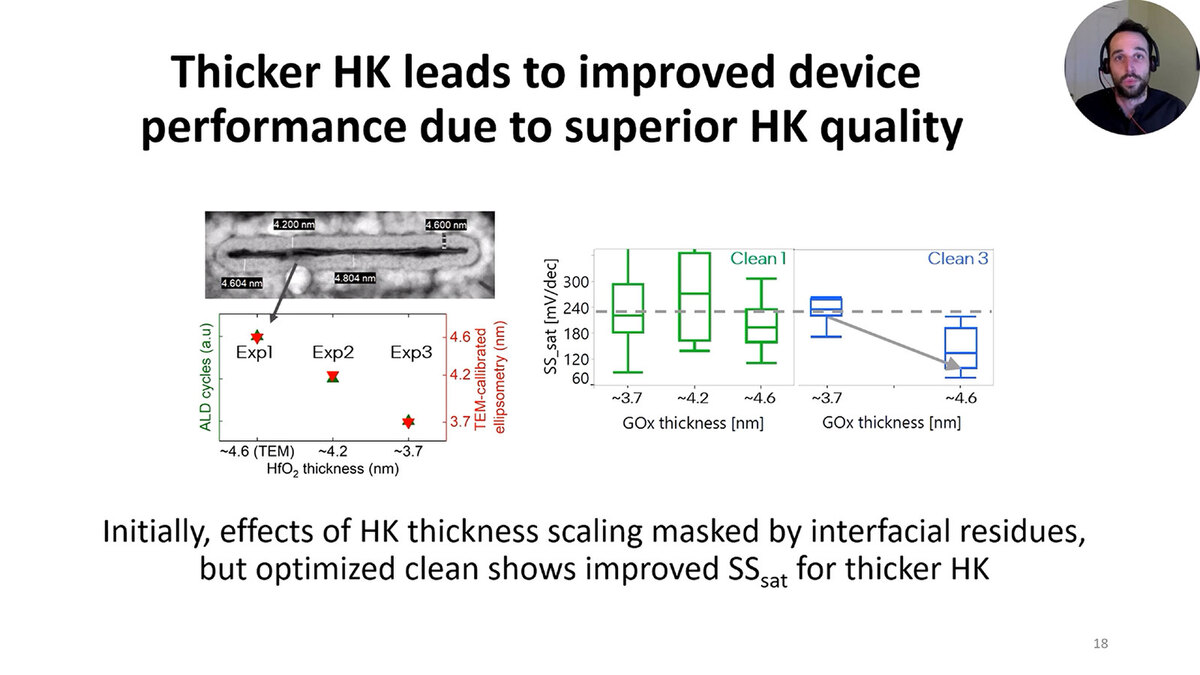

GAA NMOSトランジスタの新たな限界要因はHfO2膜の厚み

次はHfO2膜の厚みが性能におよぼす影響の比較である。HfO2はALDを使って積層するので、その回数を調整することで厚みを変化させられる。

論文では3.7nm/4.2nm/4.6nmの3種類の厚みを構成して、それぞれの特性を比較した。ここでClean 1/Clean 3は4つ上の画像と同じで、Clean 1が従来の手法、Clean 3が今回の手法だ。Clean 1の場合、膜厚を変化させてもほとんど特性が改善されない。

これは酸化膜の界面に残留した炭素汚染がEOTスケーリングを妨げたためと判断されており、逆に今回のClean 3では特に4.6nmにするとSSsatが明確に改善したが、3.7nm厚ではその改善効果が減少するとしている。Clean 1と比較して最適化が進んだClean 3でもこの限界がみられるというのは、GAA NMOSトランジスタの新たな限界要因になり得ることを示している

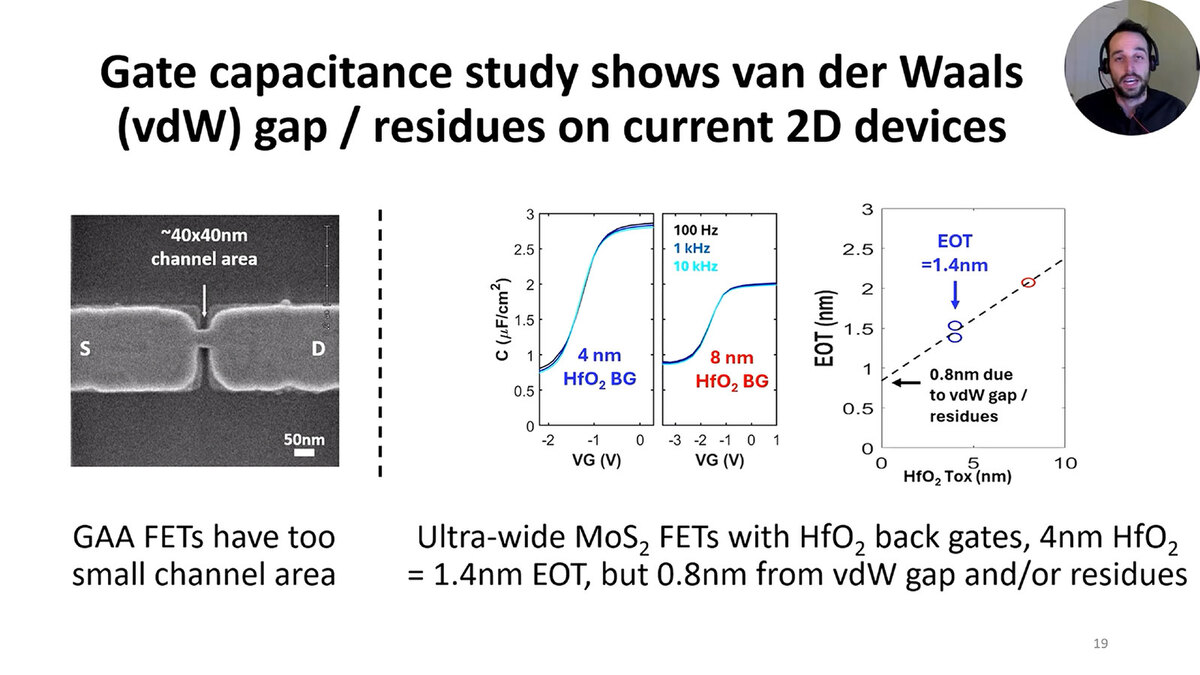

下の画像はチャネルと高誘電率酸化膜の界面に関する研究である。これはALDで構築したHfO2バックゲート基板上に、40×40nmという非常に小さなチャネルを構築し、このCV測定をした結果、4nmで1.4nm相当、8nmでは2.1nm相当のEOTになることがわかった。

ここから、vdWギャップ(van der Waals:ファンデルワールス決勝のバンドギャップ)、残留分、潜在的な剥離などが0.8nm相当のEOTになることが判明した、としている。

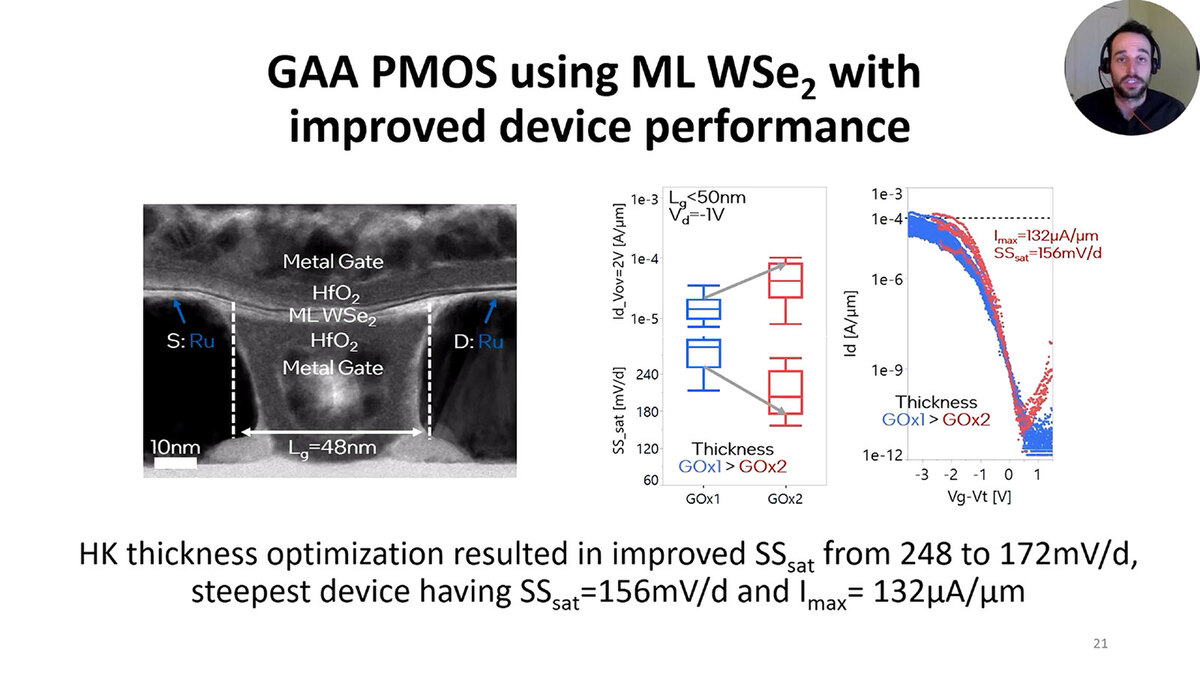

NMOSとPMOSの違い

PMOSはNMOSとは逆の傾向

ここまでの話はNMOSベースだったが、ではPMOSではどうか? ということで性能を確認したのが下の画像である。

一般論としてWSe2を利用したPMOSは、同じ構成のNMOSに劣っている。これは材料の接触抵抗と潜在的な欠陥の増加が主な課題とされている。これに対する研究の1つとして、蒸着Ru(ルビジウム)を利用したコンタクトは、Au(金)のコンタクトよりIdmaxを向上させられるという話が2023年のIEDMで発表されている。

これを一歩進め、Ruでソース/ドレインのコンタクトを形成した際の、膜厚のスケーリングを確認したのが画像真ん中のグラフである。膜厚を減らした場合、Imaxが132μA/μmにに増加し、一方でSSsatは156mV/dという記録的な値を得られたとしている。

ただこれはNMOSとは逆の傾向であり、その要因としてはNMOSとPMOSで異なる制限要因があるか、もしくはPMOSとNMOSで界面の相互作用の違いに起因する可能性があるが、これに関しては今後の研究課題としている。

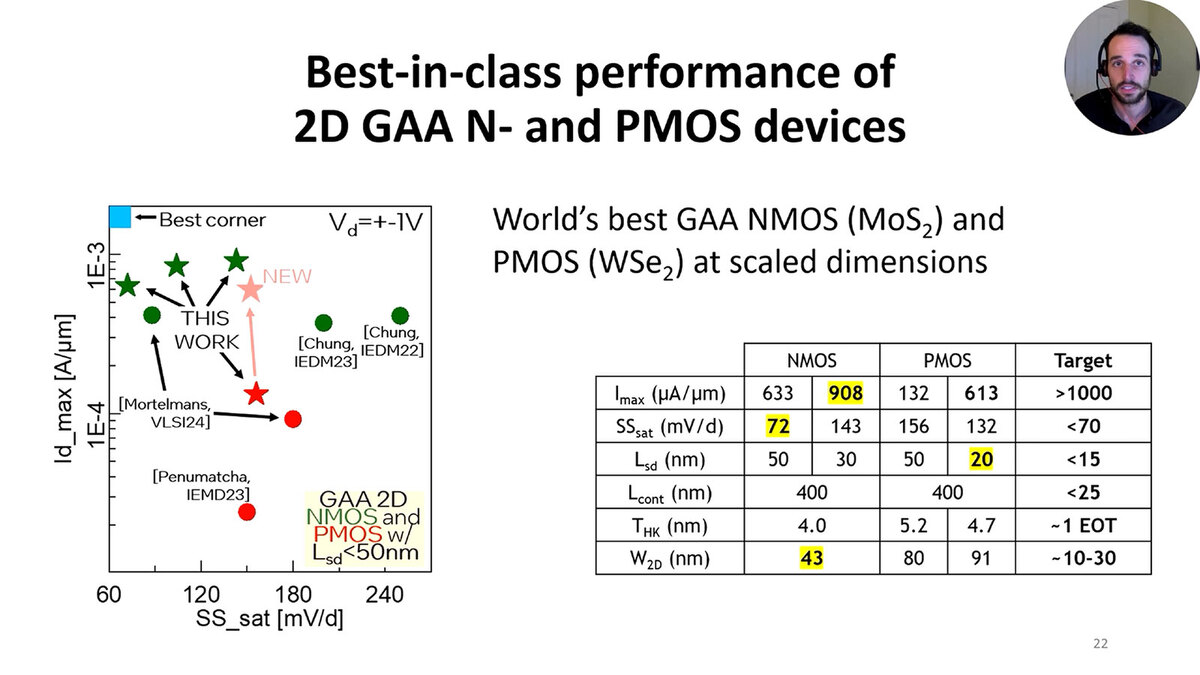

最終的な結論が下の画像で、これまで発表されたTMDベースのGAAトランジスタとしては一番良い成果を得られているが、ただしまだ目標を完全に達成できているわけではなく、今後もさらに研究を続けていくとしている。

ということで、こちらはまだ量産以前の基礎研究に近い内容であり、この成果が実際の量産製品に反映されるのはおそらく2030年以降のことになると思われる。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります