チャネル長6nmのRibbon FETが優位

それ以上でも以下でもダメ

次はShort Channelに関する検討である。Short Channel、日本語では短チャネル効果などというが、チャネルを短くするといろいろ不都合が生じることが知られている。

具体的にはしきい値電圧の低下、DIBLの悪化、サブスレッショルド係数の劣化、電流非飽和、Punch Throughなどで、これは別にRibbon FETに限らずFinFETやその前のプレーナー型のトランジスタでも発生していた事柄である(個々の説明はここでは割愛する)。

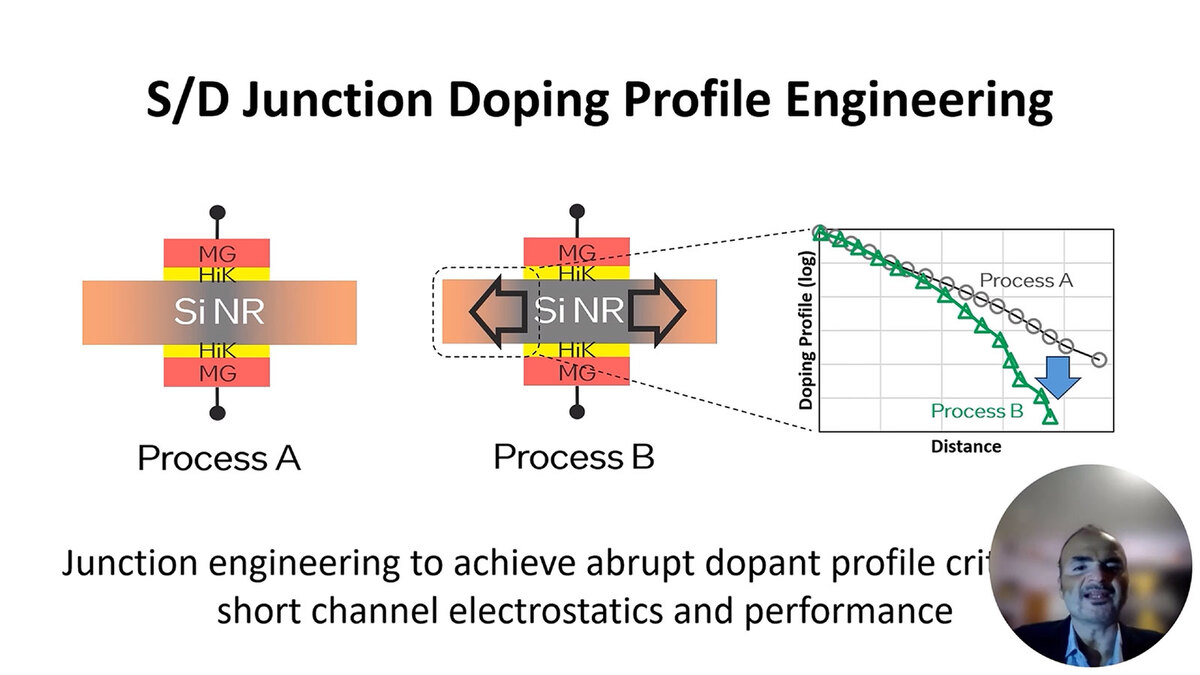

では短いとなにが発生するか? という話であるが、下の画像がこれを模式図的に示したものだ。中央のSiNR(Silicon Nano Ribbon)がチャネルそのものであり、その周囲をHigh-K素子で囲い、さらにその外側に金属ゲート(MG:Metal Gate)が存在している。

このチャネル、素子そのものはシリコンがベースであるのだが、そこに不純物をドーピングすることで特性を改良している。ところがゲート長が10nm以下になると、前述したShort Channelの問題に加え、チャネル内に残留ドーピング、つまりに均一にドーピングなされず、ドーピングが濃い部分が残ってしまう現象が発生。このドーピングにより、電荷移動量が低下することで性能が劣化する問題がある、としている。

ただしこれは適切なドーピングプロファイルを管理することで、チャネル長が10nm以下の場合でも性能を改善できるとしている(具体的にどう適切に管理するのか、は言及がない)。上の画像右のグラフは、なにもしない場合がProcess A、プロファイルを管理したのがProcess Bで、残留ドーピングを減らせることを示している。

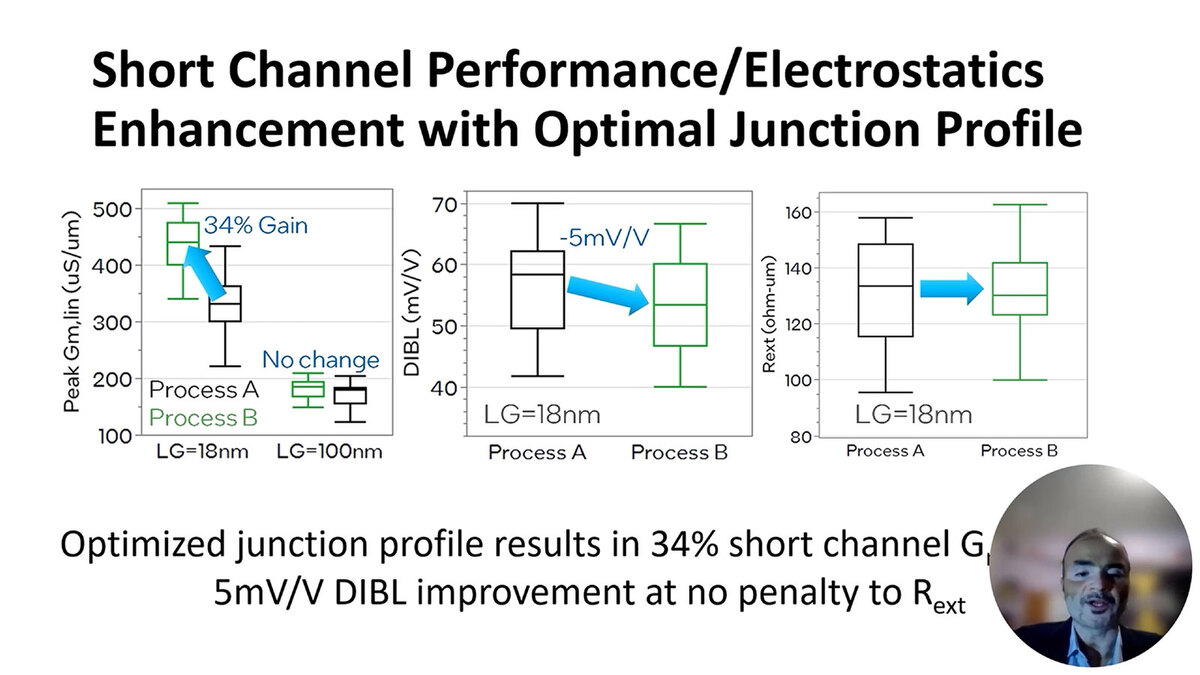

具体的にゲート長が18nmと100nmの場合で比較したのが下の画像である。一番右はトランジスタの利得を比較したもので、ゲート長100mmだとProcess AとProcess Bで違いがないが、ゲート長18nmの場合、Process BはProcess Aに対し、最大で34%の利得向上が可能になっているとする。

中央と右はゲート長18nmの状態でDIBLの特性とRextを比較したもので、Process BはRextがほぼ変わらないにも関わらず、DIBLを-5mV/V削減できた、としている。

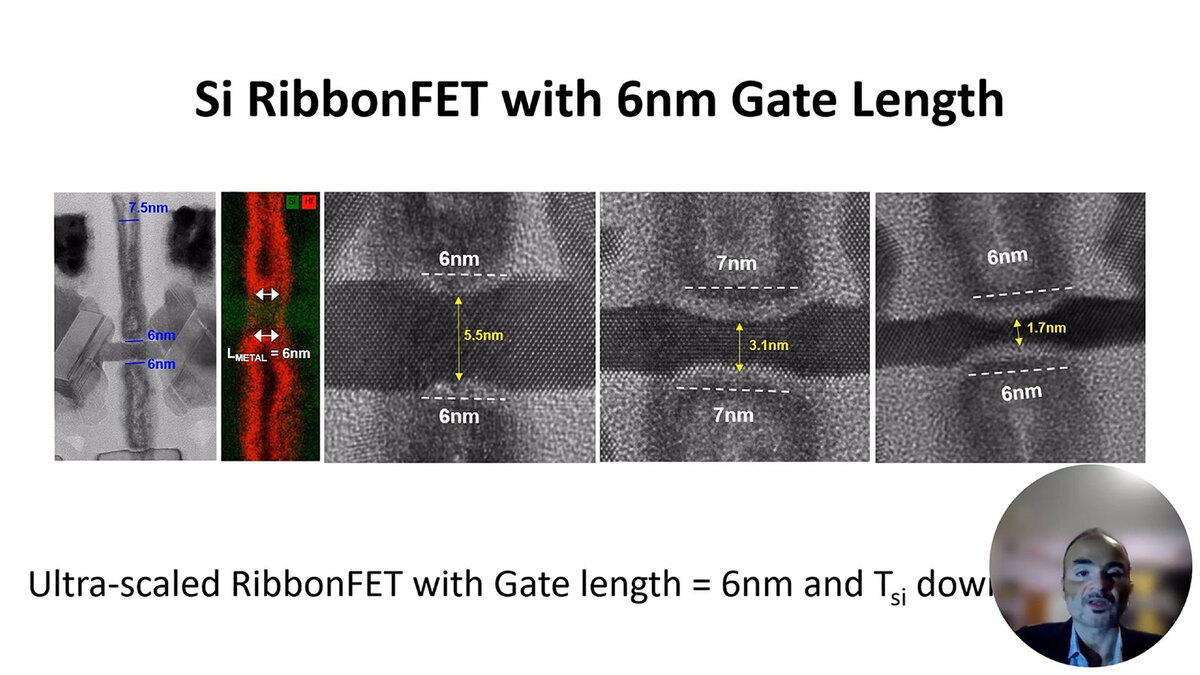

さて、18nmは100nmに比べれば短いとは言え、CPPを考えると十分に長い。今回の目的は表題にもあるように、ゲート長を6nmとしたRibbon FETの構築である。その成果が下の画像である。

左端はゲート長6nm、フィン厚み5.5nmのトランジスタのTEM(Transmission Electron Microscope:透過型電子顕微鏡)写真と、そのゲート周辺のEDX(Energy Dispersive X-ray:元素マッピングX線)写真である。説明によれば、ゲートのパターニング/エッチング工程を慎重に最適化したことで、均一なゲート長を持つプロファイルが得られた、としている。

その右にあるのが、ゲート長6nm/フィン厚み5.5nm、ゲート長7nm/フィン厚み3.1nm、ゲート長6nm/フィン厚み1.7nmという、寸法を変えた3種類のRibbon FETのTEMでの写真であり、いずれもうまくRibbon FETの成型に成功している。

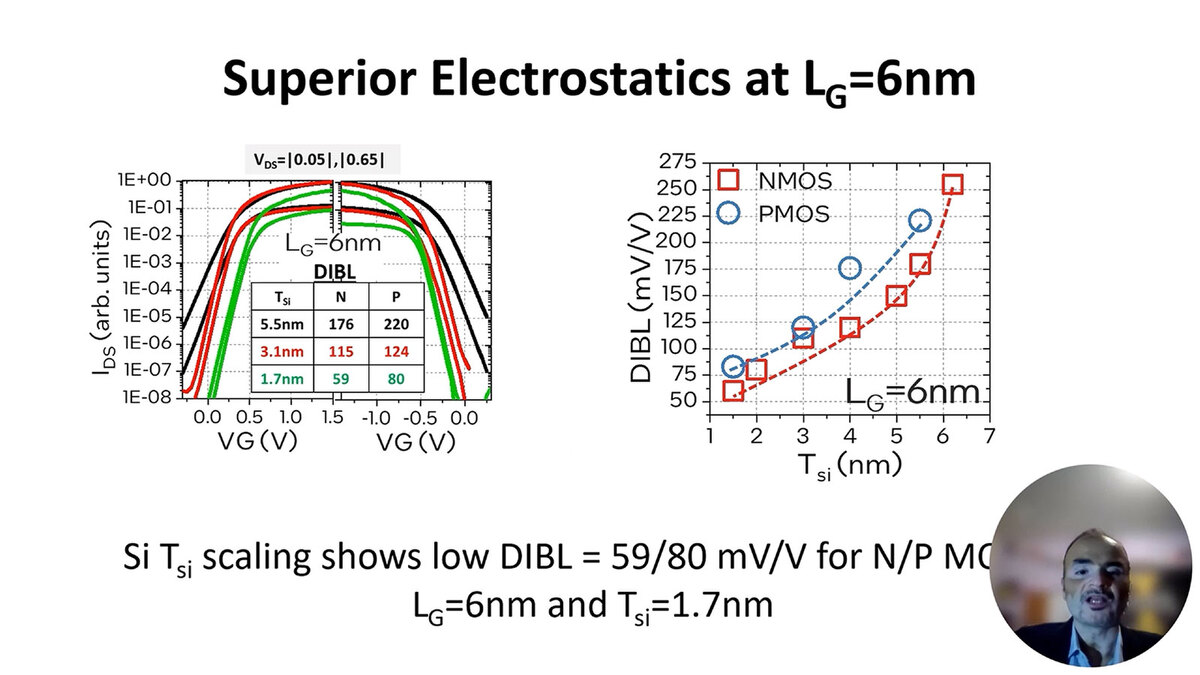

この3種類のRibbon FETについて、DIBLを測定したのが下の画像の左側である。論文によれば、フィンの厚みが5.5nmの特性は「予想通り」劣悪で、NMOSとPMOSの両方でDIBLが180mV/Vおよび220mV/Vという、Short Channel効果がモロに発揮された結果になっている。

ところがフィン厚みを3.1nmおよび1.7nmにすると、DIBLが低減されることが明確に示されている。実際1.7nmではDIBLが59mV/Vおよび80mV/Vで、5.5nmの場合のほぼ3分の1になる。3.1nmではそこまではいかないが、それでも5.5nmに比べて30~40%の低減が可能である。

この傾向を、フィンの厚みを横軸にして示したのが右側であり、NMOS/PMOSともにフィンの厚みを減らすと単調にDIBLも減っており、チャネル長が長い時にあった飽和の傾向は、このグラフからは見られないとする。

下の画像の左側はゲート長6nmの際の、フィンの厚みを変更した場合のDIBLとピークの利得をプロットしたものである。NMOSの場合は、フィンの厚みを6nm→3nmに減少させても性能へのペナルティはほとんどないが、PMOSの場合はフィンの厚みを減らすとRextが大幅に増える関係で、性能の低下が著しいとされる。

右側のグラフは、ゲート長6nmの場合における、フィンの厚みとスレッショルド電圧の関係をまとめた物である。そもそもゲート長が短いとしきい値電圧が増加する(=動作のための消費電力が増える)傾向にあるが、今回はWF(Work Function:仕事関数 金属内の電子を外部に放出させるために必要な最小の仕事量)を工夫することで、このしきい値の増加を上手く帳消しにできたとしており、厚み1.7nmの場合のしきい値は0V、3.1nmでは-0.1V弱と大幅に下げることに成功したとしている。

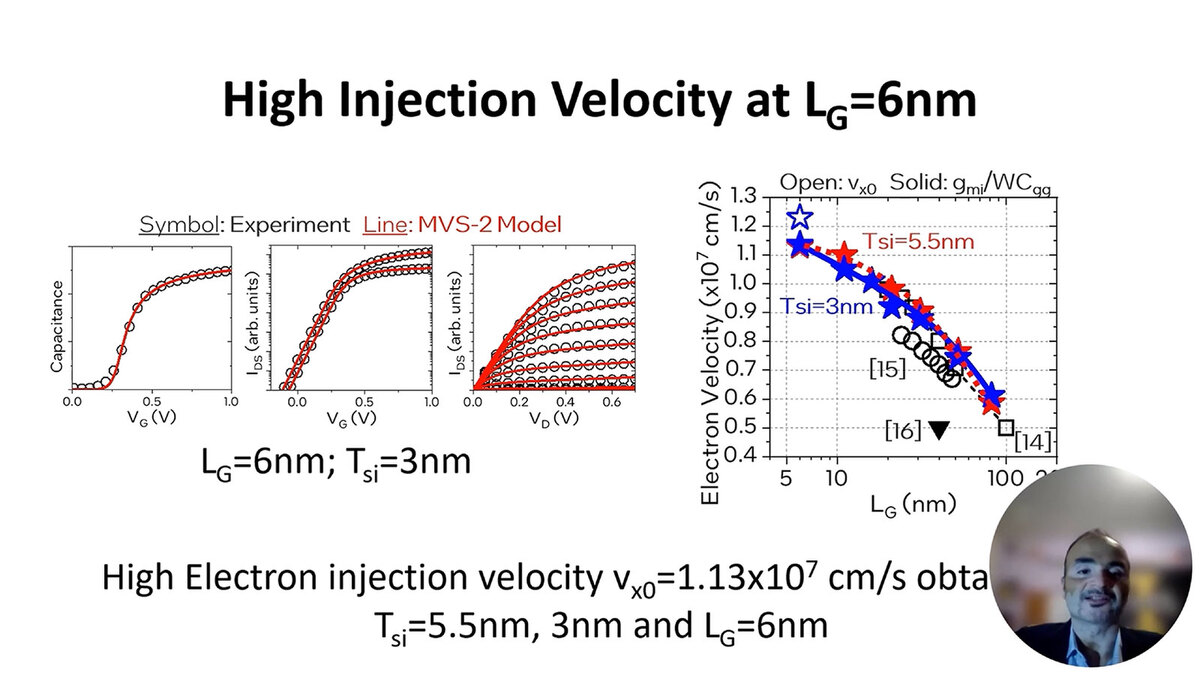

論文では最終的に、フィンの厚み5.5nmおよび3nmにおける電子注入速度が1.13x10e7cm/sになることを計測できたとしており、これはCPPが45nmのプロセスで、チャネル長6nmという短チャネルのRibbon FETが優位であることを示しているとまとめている。

この論文はあくまでもフィンが1枚のトランジスタを試作し、その特性を調査したというものであって、これが量産につながるという話ではない。おそらくこれに近い特性のトランジスタが採用されるのは相当先(Intel 6A?)になるだろうし、その頃にはRibbon FETの次のCFETに移行している頃だろう。そういう遠い未来向けの基礎研究、と考えるのが妥当だ。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります