ゲート厚を3nmより薄くすると

性能は向上しないどころかむしろ低下する

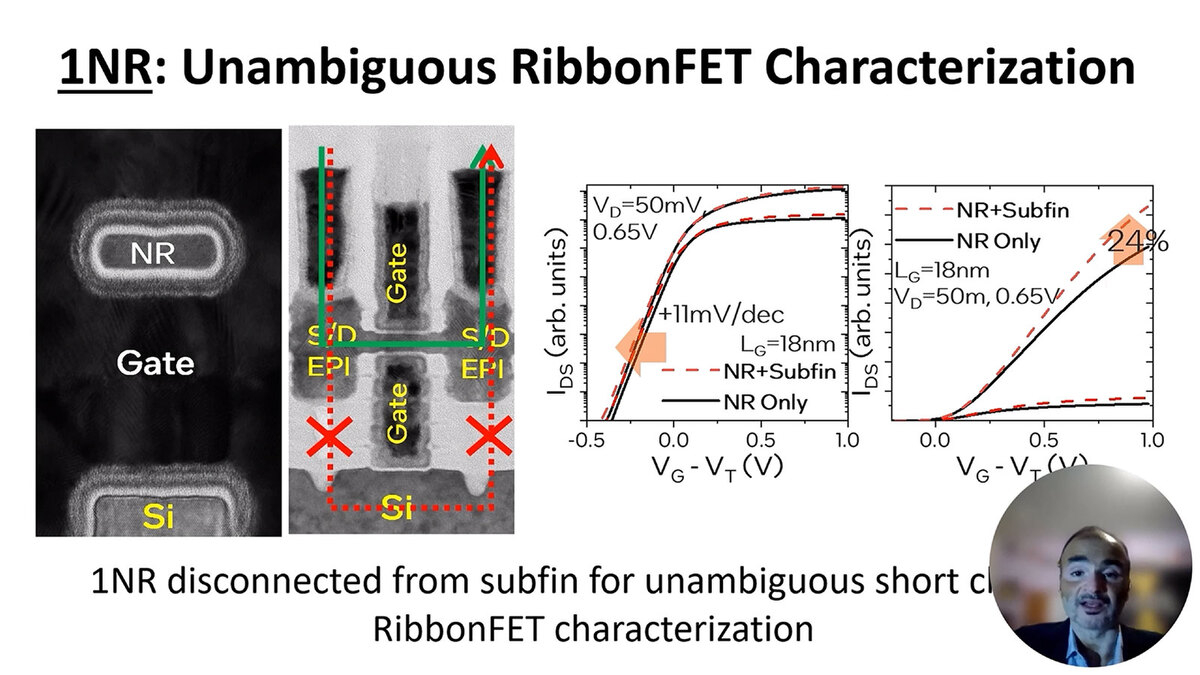

論文では実際に1NR(NR:Nano Ribbon)、つまりフィンが1枚だけのRibbon FETを構築し、その特性を測定したとしている。

実際にVg-Vt(ゲート電圧としきい値電力の差)と、その際に流れる飽和電流をプロットすると、対数軸(グラフ左側)では大差ないように見えるが、直線軸(グラフ右側)で見ると、複数フィンの場合には最大で24%ほどズレるとしており、以下のレポートはすべて1フィンのものである。この1フィンのNMOSトランジスタの性能を測定したのが下の画像である。これは言ってみればこの後の比較の基準となるものである。

Tsi、つまりRibbonの厚みは6nm、ゲート長は18nmである。左は電荷移動量で、トランジスタのスイッチング速度の指標。右はトランジスタの利得(Transconductance)のピーク値。いずれもCMOSとしてはかなり優れた特性を示している

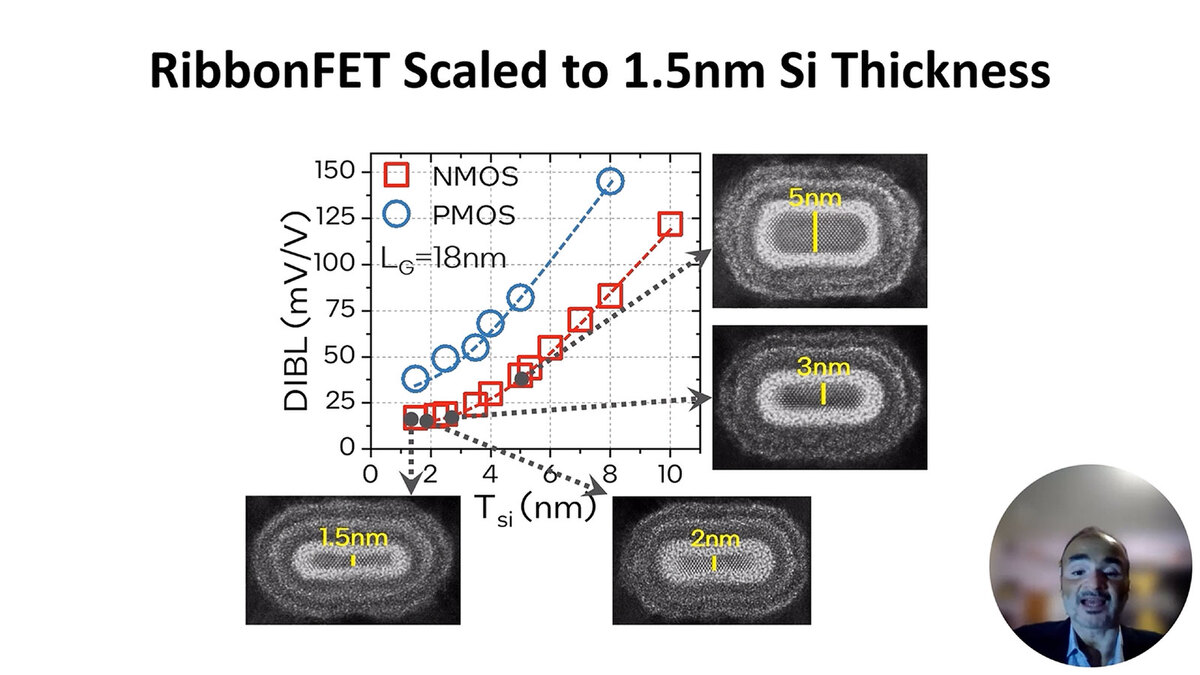

ゲート長は18nmのままにして、フィンの厚みを変更したときの特性が下の画像である。薄くするほど特性は改善することは見ての通り(DIBLは少ないほどいい)のだが、PMOSはともかくNMOSに関してはTsiが4mmあたりで特性が飽和してしまい、その先の特性改善があまり期待できないとする(PMOSは多少マシだが)。

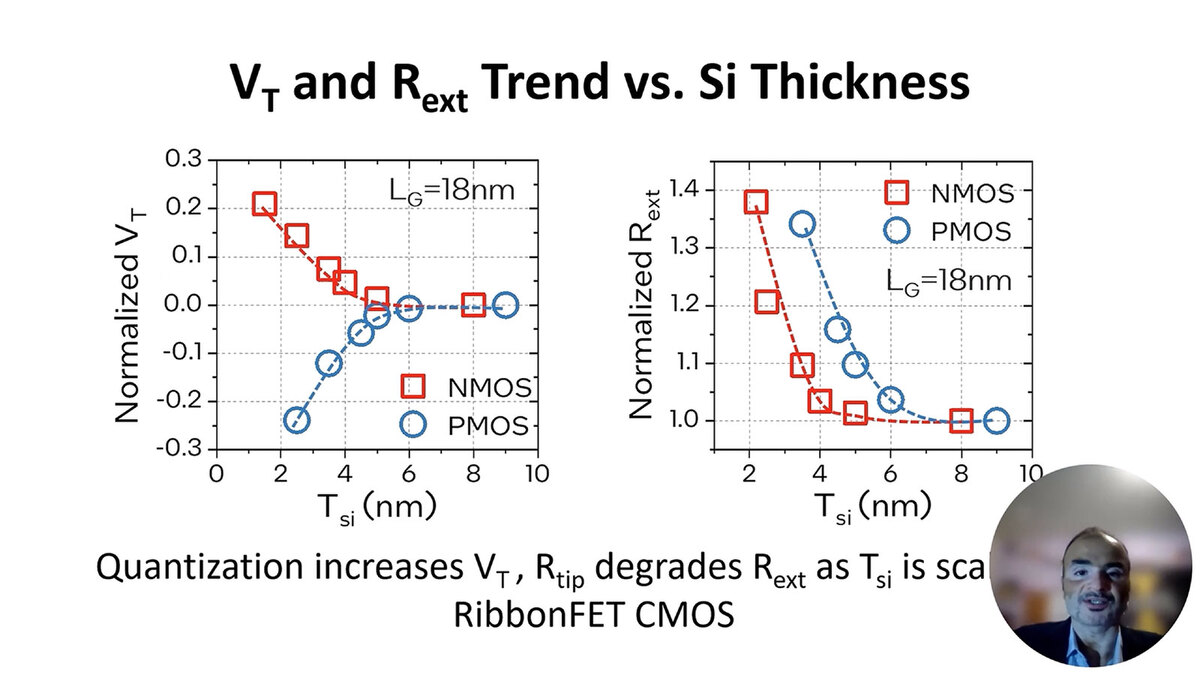

同様に厚みを変えた際のVt(しきい値電圧)とRext(外部抵抗)の推移が下の画像だ。まずVtの方は、6nmより薄くするとバラつきが次第に大きくなる。またRextについても、NMOSなら4nm未満、PMOSでは6nm未満にすると急激に抵抗値が増えるとされる。

厚みを変えた際のVtとRextの推移。Vtの方は、4nm未満になると量子閉じ込め(Quantum Confinement)によりVtが200mVほど増加する。またRextは、Finが薄くなるほどRtipが増えることで、結果としてRextが34~37%増加するとしている

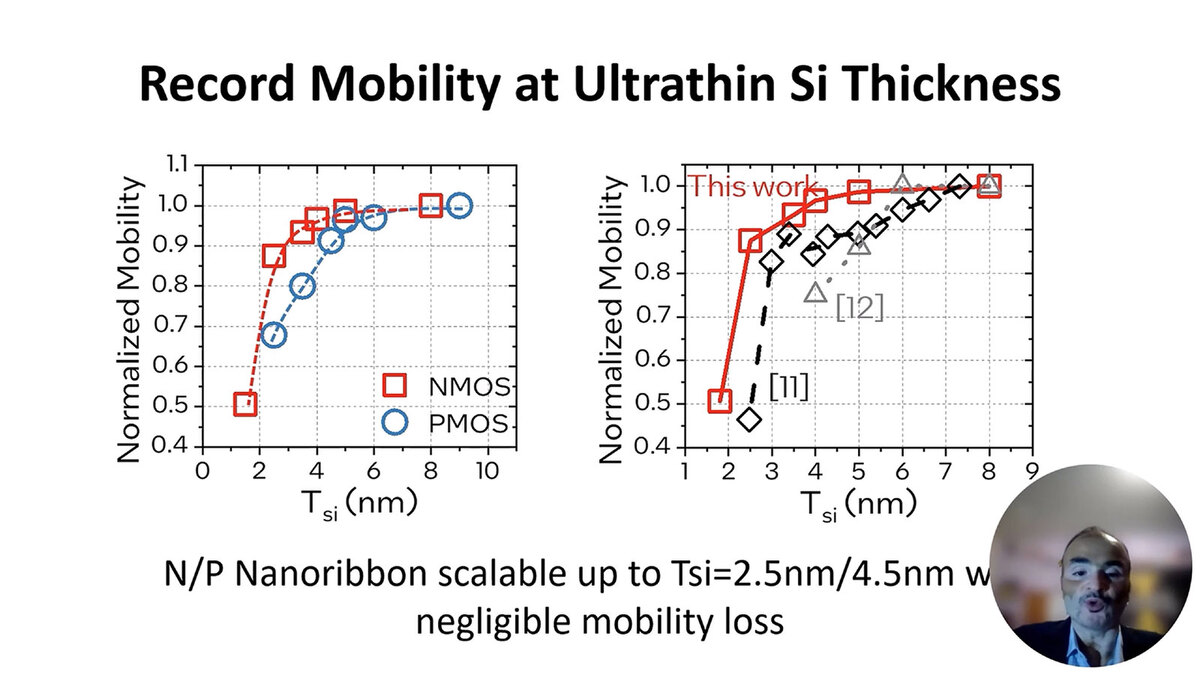

下の画像の左側は電荷移動量で、こちらも3~4nmあたりまで薄くしてもそれほど大きな損失はないとされる。右側は、過去の論文で示されたものを黒線、今回の測定結果を赤線で示した比較であるが、解説によればNano Ribbonの表面の粗さを改善したことにより、フィンの厚みが薄くなった場合でも電荷移動量が改善することを示しているとする。

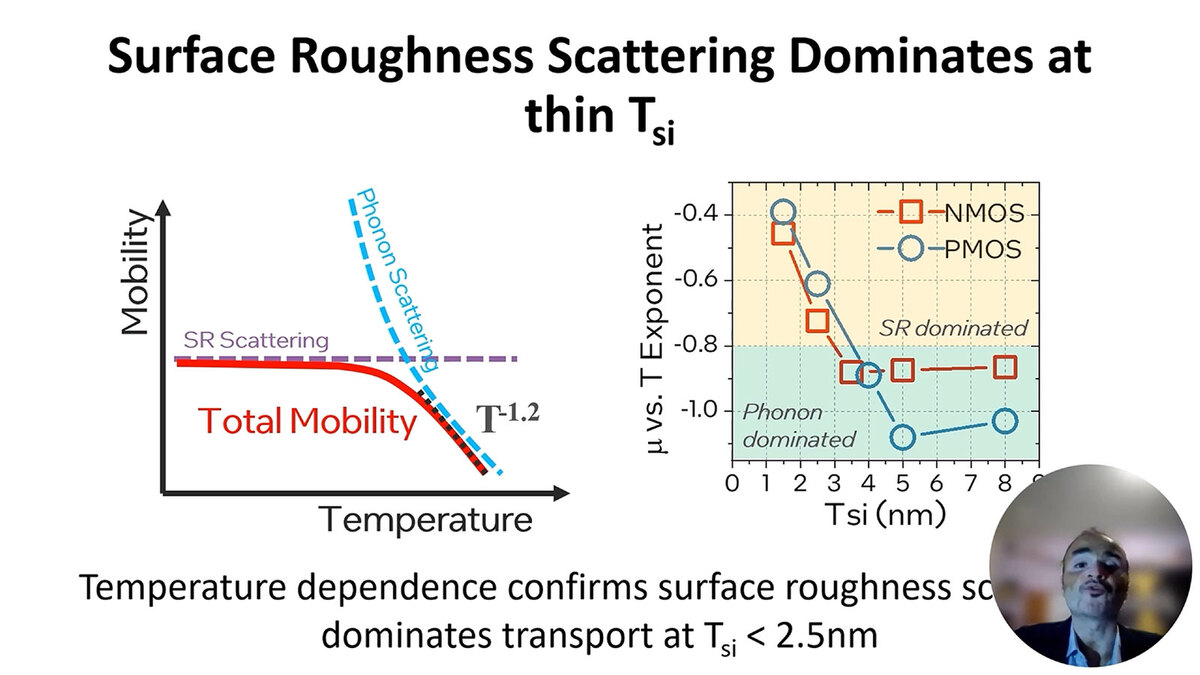

表面の粗さに関する説明が下の画像となる。ここではさまざまな温度で電界移動度を測定し、その挙動を分析することで、移動度を支配するメカニズムを導き出したとする。

左図は論文には含まれていないものだが、Phonon ScatteringとSR Scatteringの2つの点線が交わるのがちょうど3nmあたり。ただしその前から電荷移動量は低下を始めており、これが2.5nmあたりということになる

右側のグラフは、フィンの厚みが3nm以上であれば移動度を支配するのはフォノンになるが、3nm未満では表面散乱が電界移動度にとって支配的であるとする。要するにここまでの話は、フィンを薄くすれば良いというものでもなく、3nmあたりが薄くする限界であって、それを超えて薄くしても性能は向上しないどころかむしろ低下する、ということを示したわけだ。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります