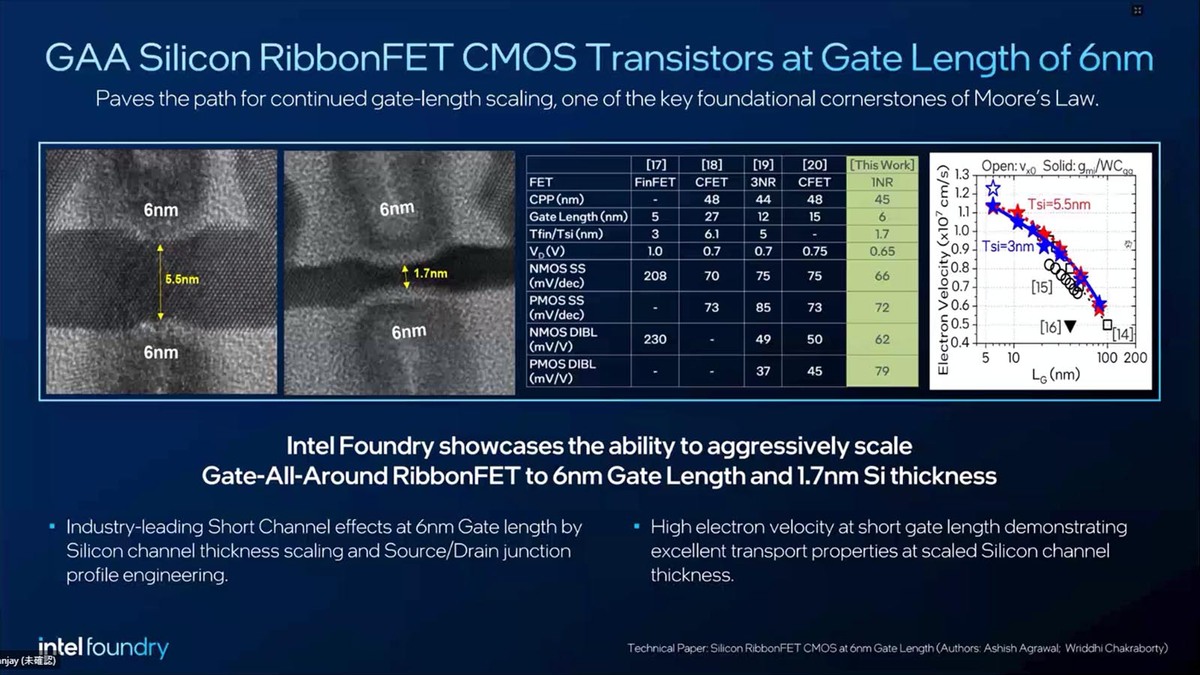

昨年12月7日~11日にかけ、サンフランシスコでIEDM(International Electron Device Meeting) 2024が開催された。IEDM 2024の第4弾は、2-1の"Silicon RibbonFET CMOS at 6nm Gate Length"を紹介しよう。インテルのプレビューでは下の画像が該当する。

RibbonFETにはゲート長6nm、フィン厚3nmが最適

この論文では、複数枚のRibbonではなく1枚だけのRibbonを構成し、その特性を調べるとともに、ゲート長およびゲートの厚みが性能に与える影響を評価し、最終的にゲート長6nm、フィンの厚みを3nmとすることで極めて性能の良いRibbonFETが構築できることを確認した、というものである。

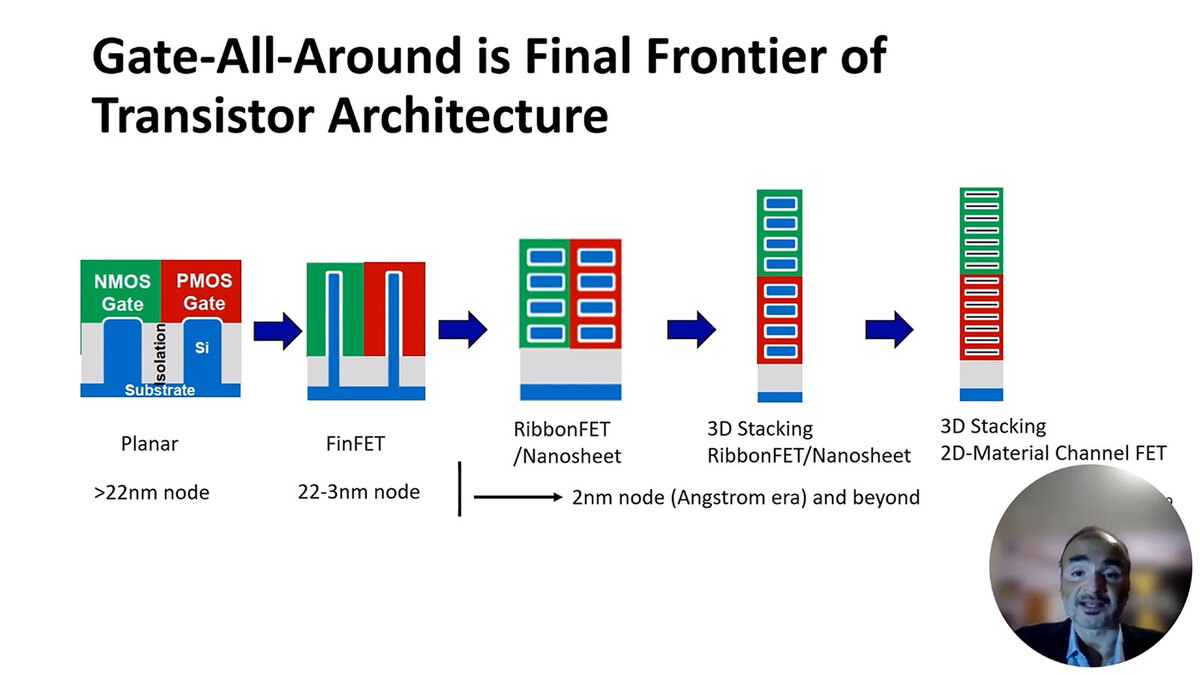

FinFET構造が使われるのは3nmあたりのノードまでで、それより微細化するにはGAA(Gate All Around)が有望であり、さらにその先はNMOSとPMOSを縦に積み重ねるCFET構造が有望、という話は連載803回で紹介した招待講演でも語られている話でもある。

こうした将来のRibbon FETに向けて今回試作したのは、ゲート長が6nmというトランジスタである。

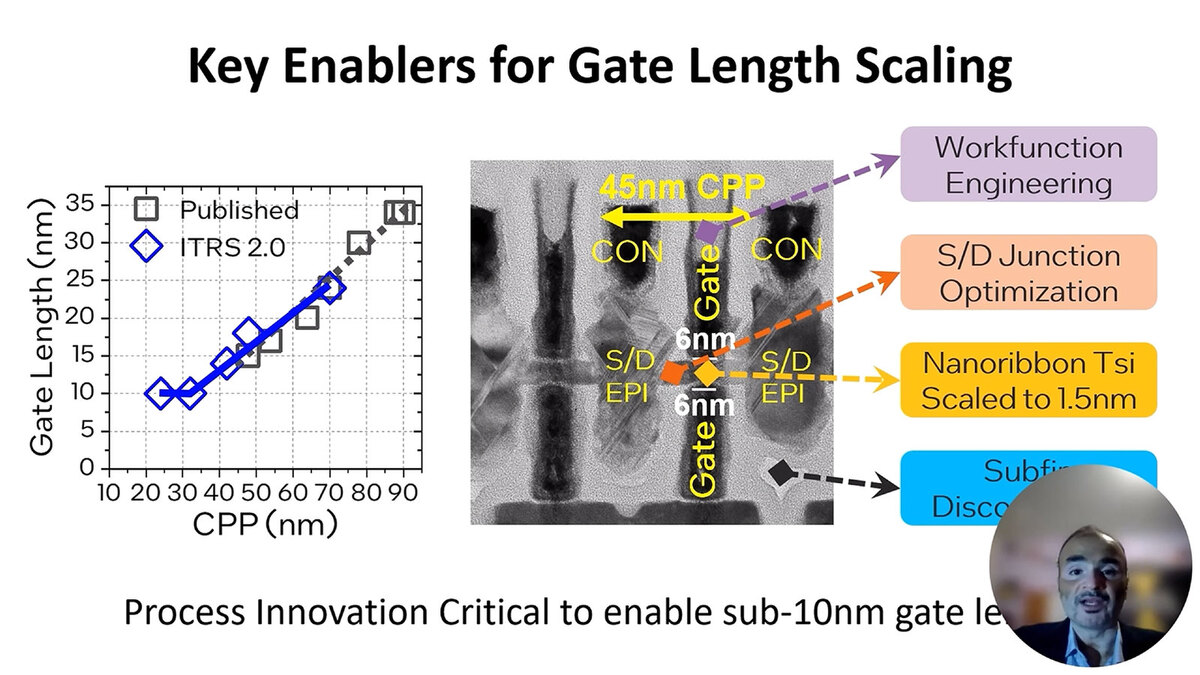

ちなみにこの中央の写真は、トランジスタを横から見たもの(下の画像でいう所の赤矢印方向)である。従来ゲート長とCPPは上の画像の左側のように、おおむね比例関係があったのだが、CPPが30nmを切ったあたりからゲート長は10nm程度で停滞していた。これをさらに短縮できる、というのが今回のポイントとなる。

黄色については後述する。Ribbon FETの図はインテルのサイトから拝借した

CPPというのは要するにトランジスタのゲート同士の間隔である。上の画像の写真は、2つのRibbon FETが並んでおり、間にSource/Drainの端子(S/D EPIはSource/Drainを構成する部分で、その上にコンタクト電極であるCONがつながっている)が入るわけだが、トランジスタの密度を上げようとすると、CPPを小さくしなければならない。

そのためにはS/D EPIを含む電極の薄型化はもちろん重要だが、もう1つはゲートの厚みを薄くすることも効果的である、とする。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります