第805回

1万5000以上のチップレットを数分で構築する新技法SLTは従来比で100倍以上早い! IEDM 2024レポート

2025年01月06日 12時00分更新

サイズの異なるチップレットを積層する新手法

Selective Layer Transfer

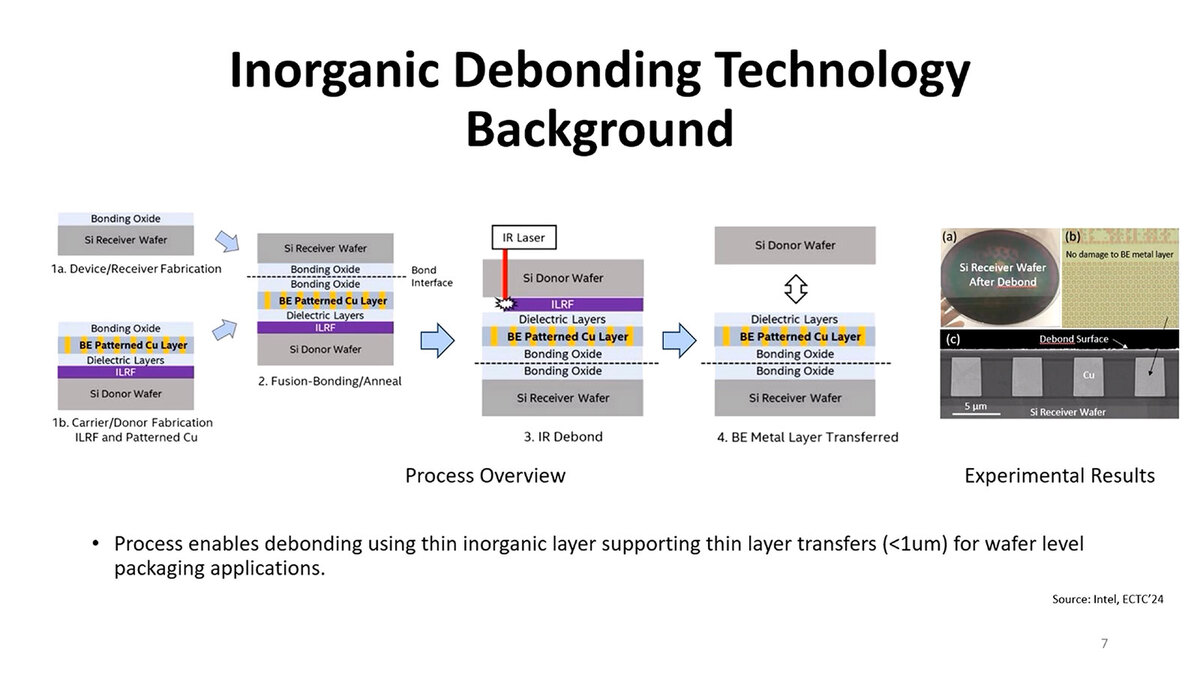

基礎となるのは、すでに利用されている技法である。2つのダイを接着するにあたり、あらかじめILRF(IR Laser Release Film)と呼ばれている非常に薄い(1μm未満)フィルムをウェハー製造時に挟み込んでおき、最後にドナーウェハーを分離したい際に赤外線を当てることで簡単に分離できる仕組みだ。

1aと1bを、Bonding Oxideが向き合うように貼り付ける。その後、赤外線レーザーをシリコン越しに照射すると、このILRFが消えてしまい、ドナーウェハー(作業用に利用しているシリコンウェハー)を簡単に分離できるというもの

オーストリアのEVG(EV Group)はこれを利用したIR LayerRelease Technologyと呼ばれる解決策を提供しているし、このフィルムについてもさまざまなものがすでに提供されている。これを利用して、サイズの異なるチップレットを積層しよう、というのが今回の内容だ。

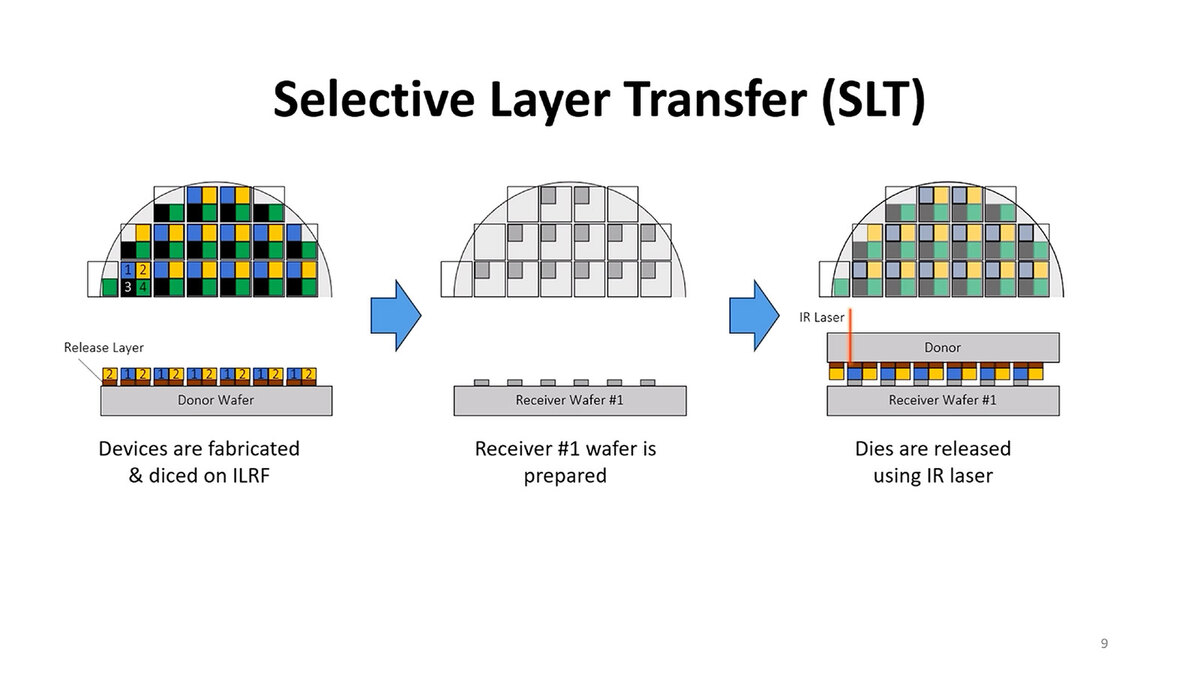

まず一番左がチップレットを構築したウェハーであり、#1~#4の4種類のダイがある。真ん中がそのチップレットを載せるレシーバーウェハーで、ここでは#1のチップレットを載せる用意がなされている。

右が実際に載せる際の手順で、ドナーウェハーをひっくり返してレシーバーウェハーの上に被せる。この状態で、ドナーウェハーの上からダイ #1の底の部分にだけ赤外線レーザーを当てると、そこだけフィルムがなくなり、ダイ #1がレシーバーウェハーに残る。

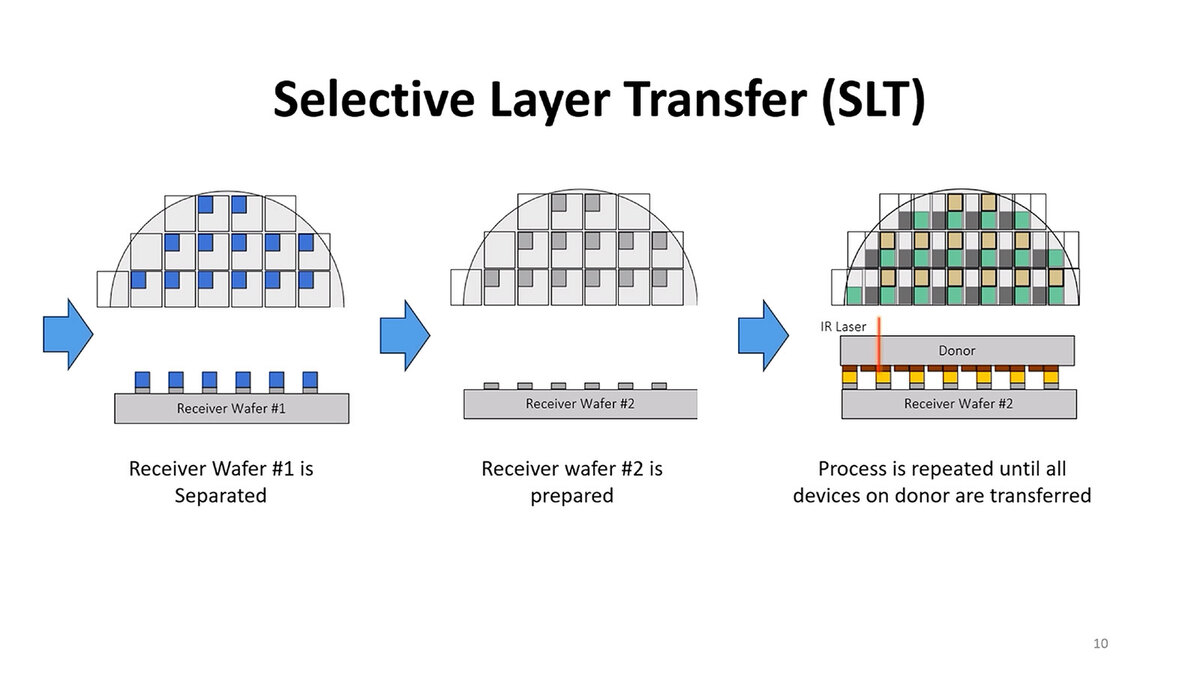

あとはレシーバーウェハー #1を取り外し、同じように今度はダイ #2を別のウェハーに載せるという形で、チップレットを全部転送できることになる。

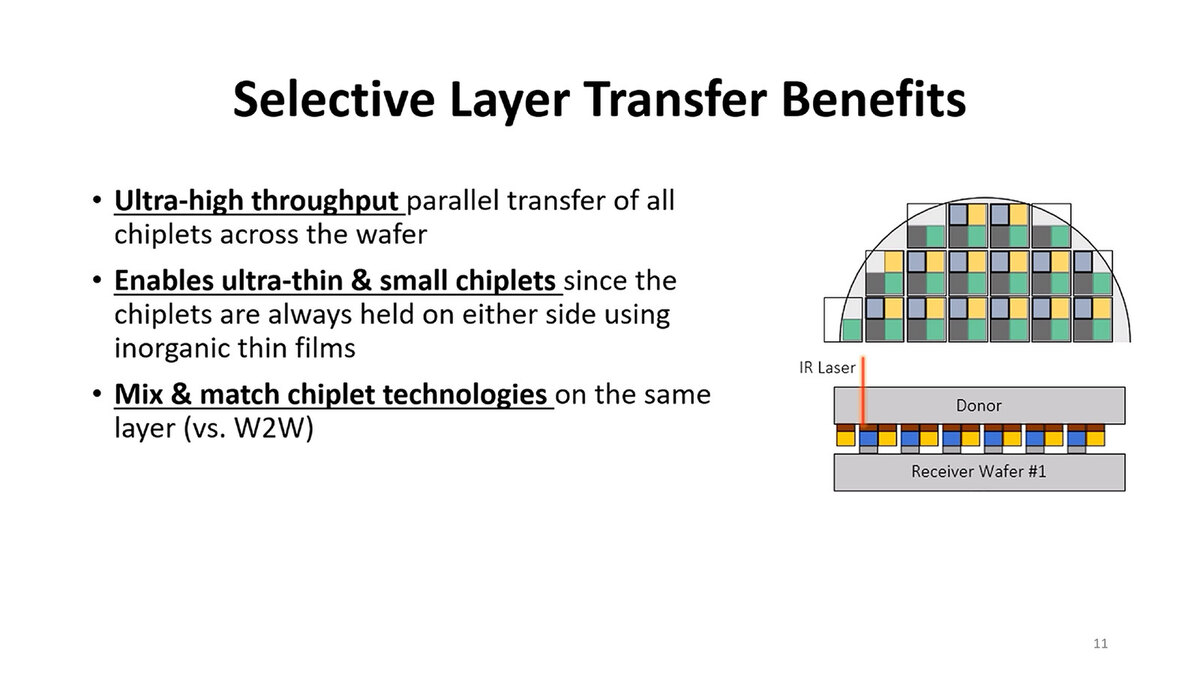

この方式のメリットはいくつかあり、当然スループットが早い(位置合わせの手間がチップレットの種類の数だけで済む)し、小さなチップレットであっても問題なく積層できる。

この後は、普通に誘電体を充填し、その上層にインターコネクトを積層することで完成である。これをもう少し応用すると、右側のように大規模なAIアクセラレーターを組み合わせたチップにしたり、あるいはIoT向けのチップをチップレットで作ったりすることも可能になる。

そもそも現在チップレットではあまり小さなサイズのダイを組み合わせることがない。これはダイサイズがある程度小さくなると、モノリシックで製造する方がトータルコストが安くなることに起因する。

ダイサイズを小型化することによる歩留まり向上や、最適なプロセスを使うことによるダイサイズの最小化に起因するコスト削減より、チップレットを構築、検査するための追加コストの方が大きくなるからである。

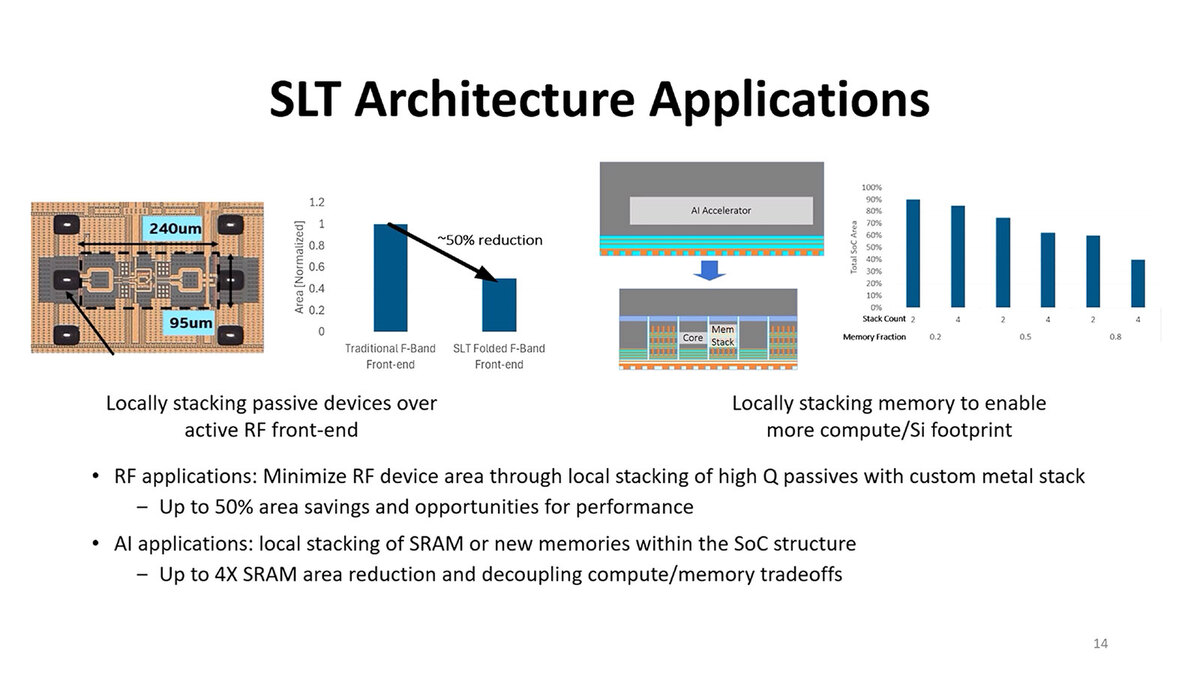

検査はともかくとして、製造に関しては今回の手法を使うと大幅に下げられる可能性が出てくる。実際、簡単な試算ではあるが、例えばIoTなどに向けたRFフロントエンドでは50%以上の面積削減が可能だし、AI向けアプリケーションプロセッサーでもSRAMをどんどん積層することで大幅に面積削減ができる。

前回も触れた検査コストをどうするのか? という問題は残る(この論文はそこには踏み込まず、あくまで製造工程にフォーカスしている)ものの、大幅にチップレット構築のコストを下げられる可能性があるというのは、よりチップレットの普及を促進する要因になるだろう。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります