第777回

Lunar Lakeはウェハー1枚からMeteor Lakeの半分しか取れない インテル CPUロードマップ

2024年06月24日 12時00分更新

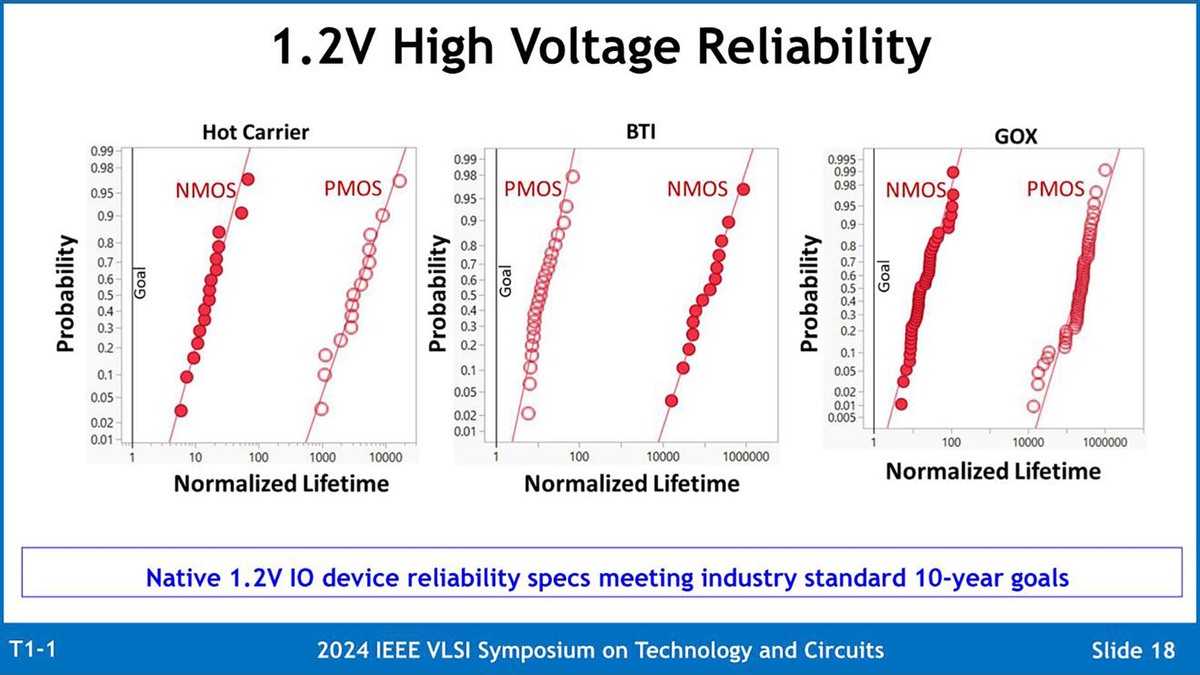

Lunar Lakeは3nmプロセスのN3Bを採用

Intel 3はネイティブ1.2Vで動作するトランジスタを追加でサポートするのだが、その1.2V出力トランジスタの信頼性が「業界標準である動作寿命10年をサポートする」と書いてあり、逆に言えばIntel 4までの通常電圧トランジスタの寿命は? となるわけだ。講演では当然そのあたりには触れていない。

言ってみればIntel 4はIntel 3の先行試作プロセス的な位置付けと考えるのが妥当だろうし、そうであればMeteor LakeしかIntel 4を使わないというのも納得できる。

したがって、本来ならIntel 3あたりを使いたかったのだろうが、こちらはXeon 6向けにまず予約が入っており、Lunar Lakeの量産に使えるほどのキャパシティがなかったのだろう。それでも他に使えるプロセスがなければ、Xeon 6の量産スケジュールを調整するなどして無理やり突っ込むしかなかったのだろうが、ここで幸運にもTSMCのN3Bが空いていた。

TSMCのN3BはTSMCとしては3nmの最初のプロセスで、2022年末に量産がスタートするものの、当初全量をAppleが予約していた。ところがこのN3B、歩留まりが非常に悪いという欠点を抱えており、それもあってAppleは途中でこのN3Bプロセスの契約を解除し、Apple自身もN3Eプロセスへ移行した、という話は昨年10月に話題が出ている。

N3EはN3Bの改良型というか、本来は廉価版という位置づけであり、N3Bが25工程でEUV(極端紫外線)を利用するのに対し、N3Eは19工程に削減。さらに配線層をダブルパターニングからシングルパターニングに改めたという話が聞こえてきている。

ちなみにこのダブルパターニングからシングルパターニングへの更新、さすがに全配線層ではないだろうとは思うが、配線がN3Bより太くなったものと思われる。そもそも一般論としてM6やM7以上なら普通はシングルパターニングで実装できるからだ。

その分実装密度が下がりそうな気もするのだが、結果から言えば歩留まりが大きく向上(N3Bは試作段階での歩留まりが55%程度だったが、量産に入ってからも60%台だったという話を聞いている:N3Eは試作段階からもっと歩留まりが高かった)し、ダブルパターニングの廃止やEUVの工程数削減などで生産コストも下がり、それでいてなぜか性能も上ったそうで、それはみんなN3BよりN3Eを使いたがるわけである。

この結果N3Eは大人気であり、AMDですら今年提供できるN3Eプロセスの製品はTurinベースのEPYCだけで、Ryzenなどは引き続きN4での提供となっている。本当ならインテルもN3Eを使いたかったのかもしれないが、こういう事情で利用は不可能である。そこに来てN3Bの生産枠が余っているという話であれば、歩留まりの低さには目をつむってでも使わざるを得なかった、というあたりが正確なところかもしれない。

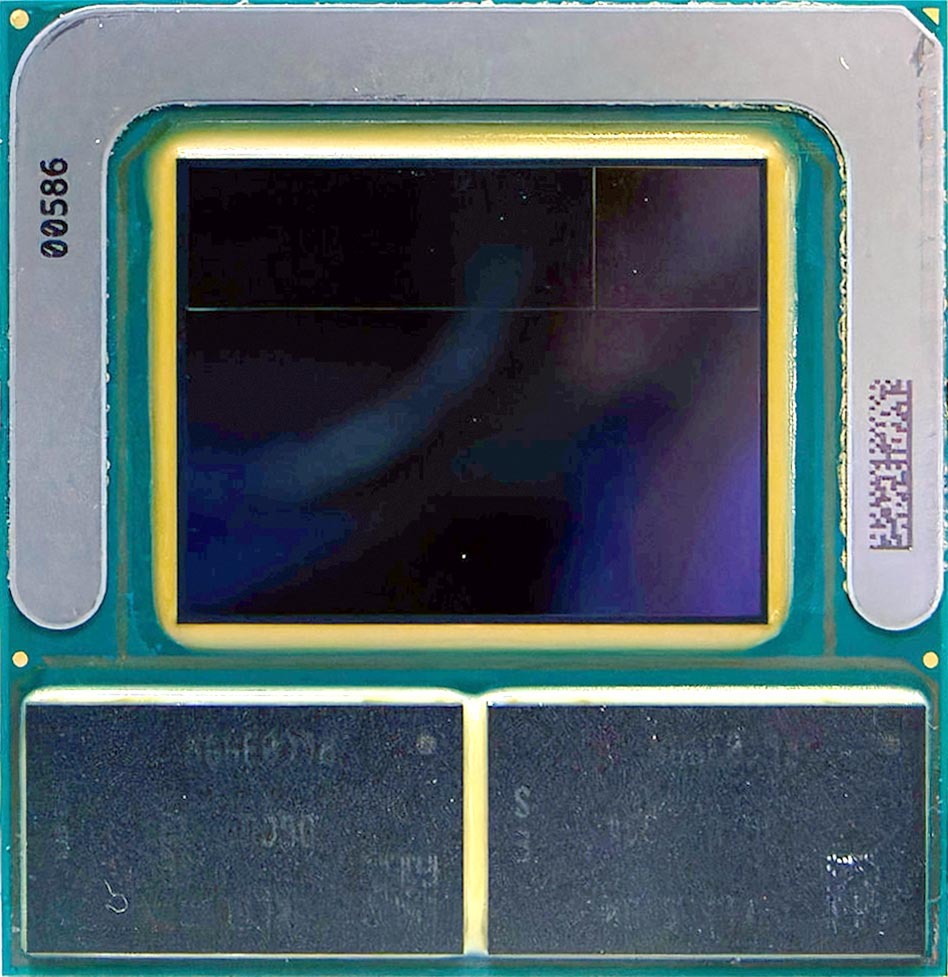

ただ実はこれ、けっこう厳しい話である。Lunar Lakeのパッケージはほぼ正方形に見えるが、微妙に縦長(27×27.5mm)である。なぜわかったかというと、パッケージに搭載されているLPDDR5Xの寸法が7×12.4mmだからで、ここからの推定である。

Lunar Lakeのパッケージ。JEDECではLPDDR5/5Xの寸法をJESD209-5で規定(最新のものはJESD209-5C)しているが、寸法が複数あるので、どれなのかを探し当てるのに苦労した。写真の輝度を上げているので、タイルの切れ目がわかる

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります