第774回

日本の半導体メーカーが開発協力に名乗りを上げた次世代Esperanto ET-SoC AIプロセッサーの昨今

2024年06月03日 12時00分更新

ET-SoC-2は予定通りなら2025年後半にサンプル出荷開始

次世代のET-SoC-3は2026年後半出荷とのことだが間に合うのか?

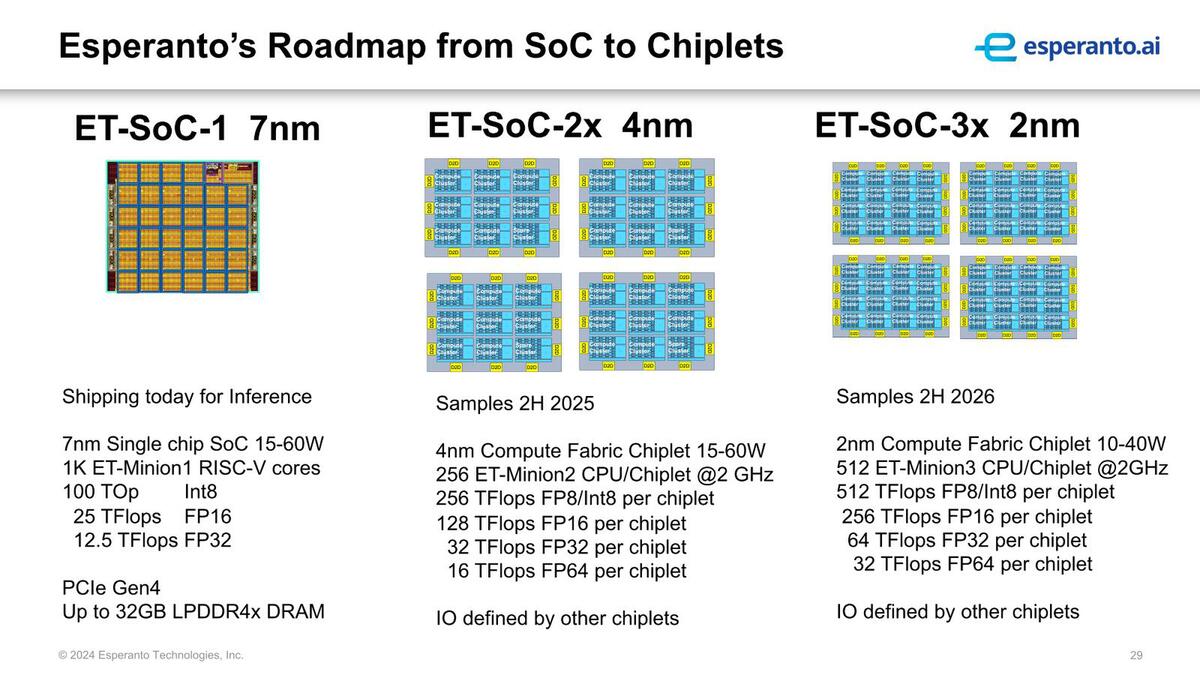

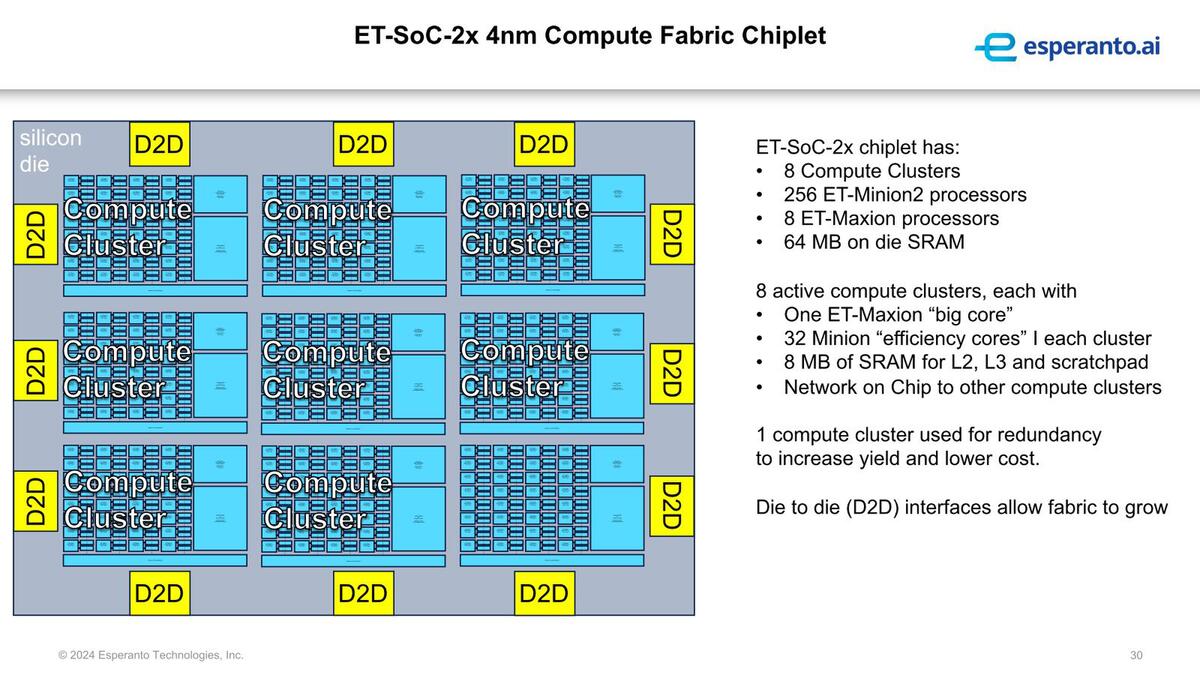

さてここからが将来製品のロードマップである。ET-SoC-1はチップ内にすべての機能を搭載しており、ここにはPCIeやメモリーコントローラーなども含まれていたが、ET-SoC-2以降はすべてチップレットになり、I/O類やメモリーコントローラーなどは外部のチップレット任せとなる。

ET-SoC-1では1088個だったET-Minionが、ET-SoC-2ではチップレット1個あたり256個になる計算で、ほぼ4分の1に減るわけだが、性能は4倍になるから「同じ動作周波数ならば」性能は同等と言う計算だ。

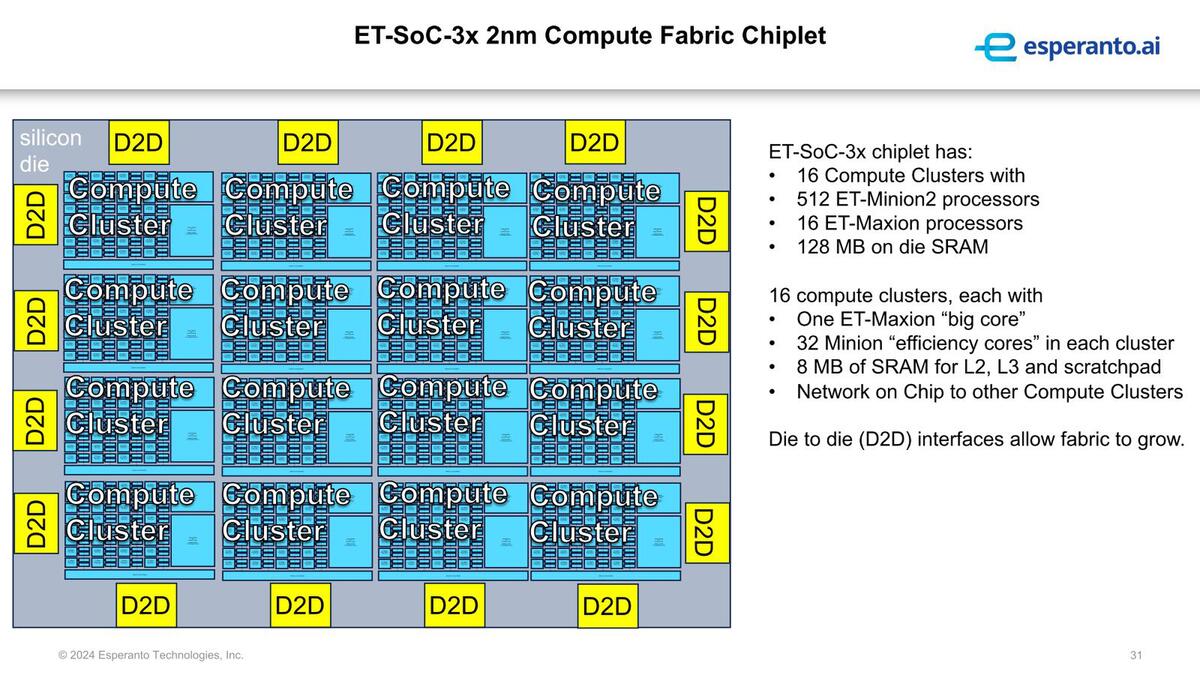

ちなみに上の画像で示すように、ET-SoC-2は9クラスター(うち有効なのが8)、ET-SoC-3は16クラスターとなる。クラスター内部に関してはET-SoC-2とET-SoC-3で基本的には同じ、という話であった。ただET-SoC-2は12個のDie-to-Die I/Fを持つ一方、ET-SoC-3は16個となる。

ET-SoC-2は12個のDie-to-Die I/Fを持つ。このD2D I/Fがどこにつながるのかがはっきりわからないが、おそらくクラスター同士をつなぐNoC(Network on Chip)に接続されるのだろう

Die-to-Die I/FはUCIeを利用しており、転送速度は32Gbpsとのこと。0.2~0.3pJ/bitで、1Tbitのリンクでも消費電力は0.5W程度との試算が出ている。

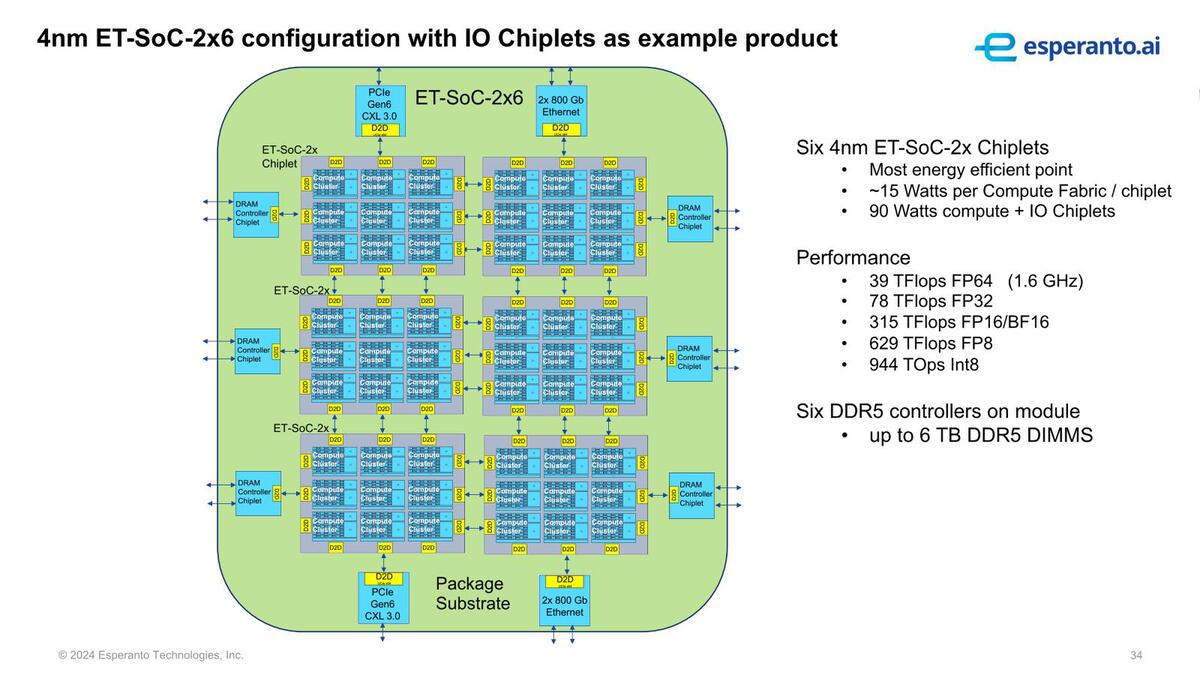

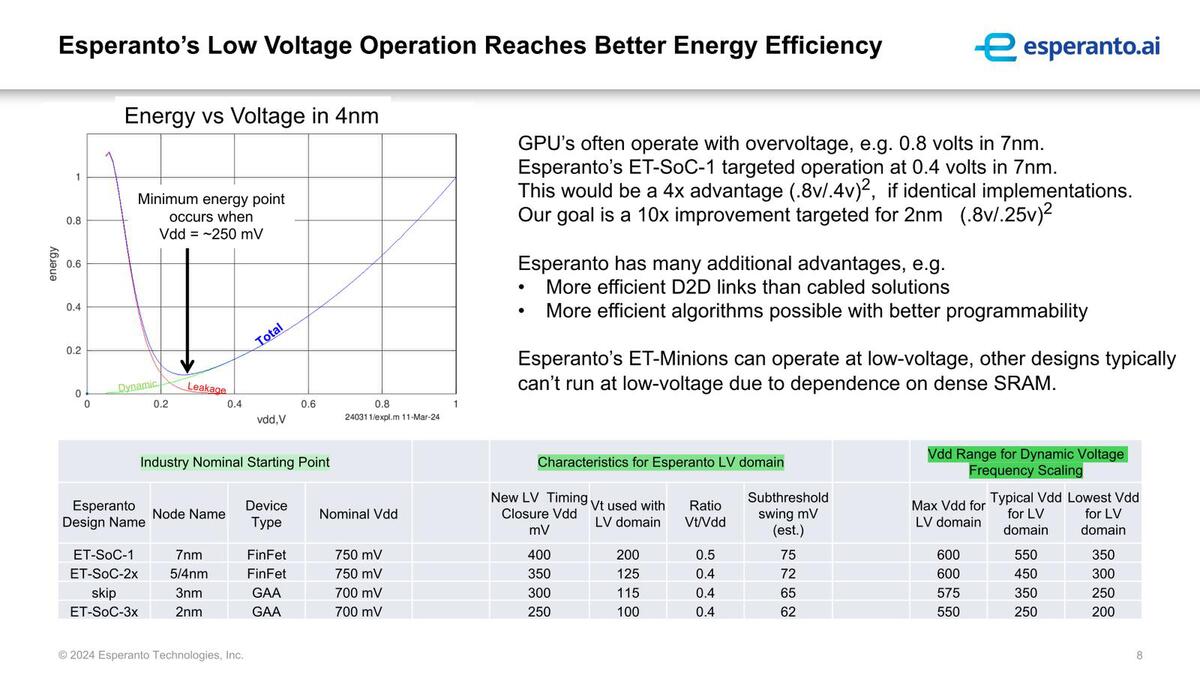

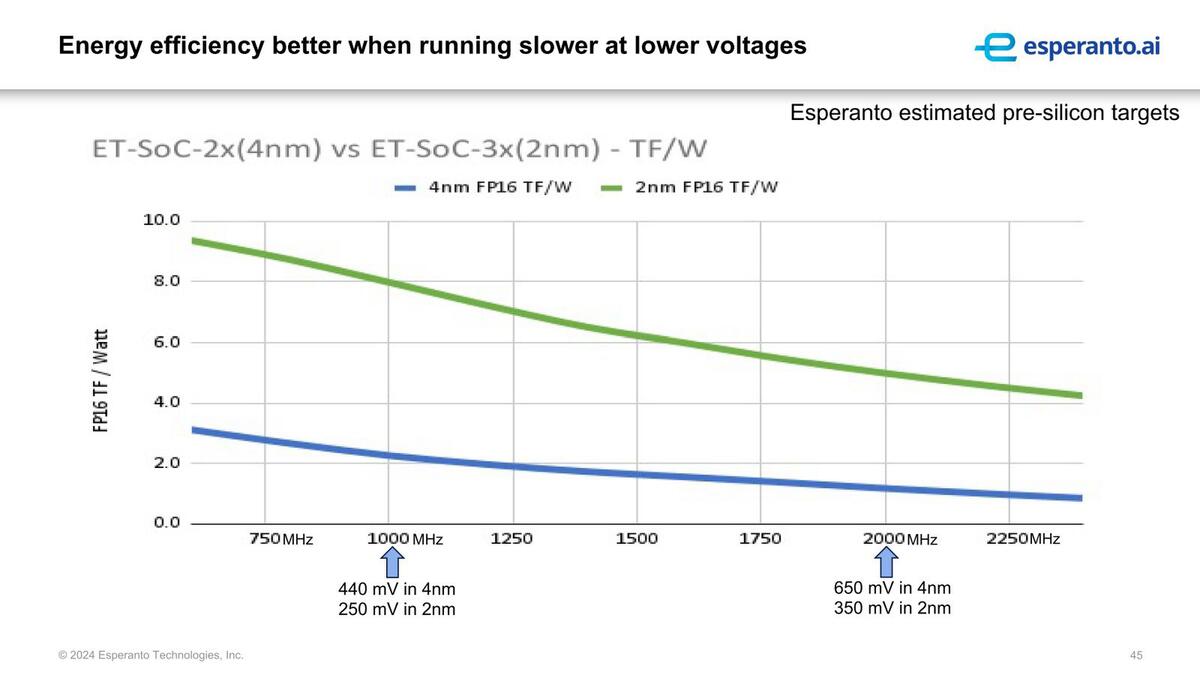

1GHz動作だと4nmが2.2TFlops/W。ET-SoC-2が1GHzで65.5TFlopsなので、消費電力はおおむね30W程になる計算だ。ET-SoC-2は133.1TFlopsだが、こちらは8TFlops/Wになるから消費電力は16W強まで落ちる

気になる動作周波数と消費電力であるが、推定で言えば1GHz動作が4nmで440mV、2nmなら250mV程度で可能になる、としている。また2GHz動作ではそれぞれ650mV/350mVということで、この2GHzの数字はわりと普通で、通常の4nmよりやや低い程度であり、ELVのメリットがまるで生かせない。おそらくは1GHz動作が標準的な数字ということになるだろう。

ただ実際の構成案を見ると、これでもまだ消費電力が多すぎる。実際には350mVあたりまで下げることを想定しているようだ。

話が前後するが、Esperantoでは第2世代のET-SoC-2を4nm、第3世代のET-SoC-3を2nmで製造することを予定している。このうち第3世代は冒頭で述べたようにRapidusで製造されるのだが、第2世代はどうもSamsungのSF4が利用されるようだ(SF4Eかもしれないが、そこまでは確認できなかった)。

まだET-SoC-2はテープアウトに至っていない(もうすぐらしい)が、2025年後半にはサンプル出荷を予定している。それはいいのだが、ET-SoC-3は2026年後半のサンプル出荷としている。Rapidusの正式なオペレーション開始は2027年度であることを考えると、さすがにこれは厳しくないだろうか? というのが正直な感想である。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります