富士通、量子シミュレーターの量子回路計算を200倍高速化する新技術

2024年02月19日 16時30分更新

富士通は2月19日、量子シミュレーター上で、量子コンピューターの初期の使用方法として提案されている量子・古典ハイブリッドアルゴリズムを、従来のシミュレーション所要時間と比較して200倍高速に実行できる技術を開発したことを発表した。

誤り耐性量子コンピューター(FTQC)の開発が世界的に進む一方で、FTQCに先んじて量子コンピューターの有用性を示すため、100から1000量子ビットの小・中規模でノイズを許容する量子コンピューター(Noisy Intermediate-Scale Quantum Computer、NISQ)向けの実応用の検討も進められている。

同社は代表的なNISQ向けのアルゴリズムである変分量子固有値ソルバー(VQE)を応用することで、量子アプリケーション開発のための量子シミュレーターを開発し、量子回路計算そのものの高速化に取り組んできた。しかしVQEは、問題の規模の増大に伴い量子回路計算の繰り返し回数が増加するため、大規模な問題では数百日程度かかることもあるという。そのため、実用に向けた量子アルゴリズムの開発が課題だった。

同社はこの問題に対し、繰り返し実行される量子回路計算を複数同時に分散処理し、さらに精度の劣化を抑えて量子回路計算量を削減することで、200倍の高速化を実現する技術を開発した。

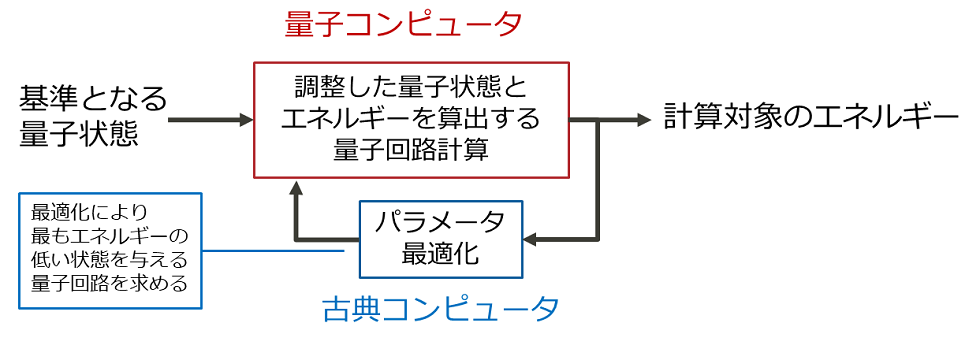

量子・古典ハイブリッドアルゴリズムでは、量子回路計算を実行する処理と、古典コンピューターを利用して量子回路のパラメーターを最適化する処理を交互に繰り返すことで、最もエネルギーの低い状態、例えば分子の基底状態を与えるような量子回路を求めている。しかし、問題規模が大きい場合膨大な計算時間が必要となるため、新たな技術が求められていた。

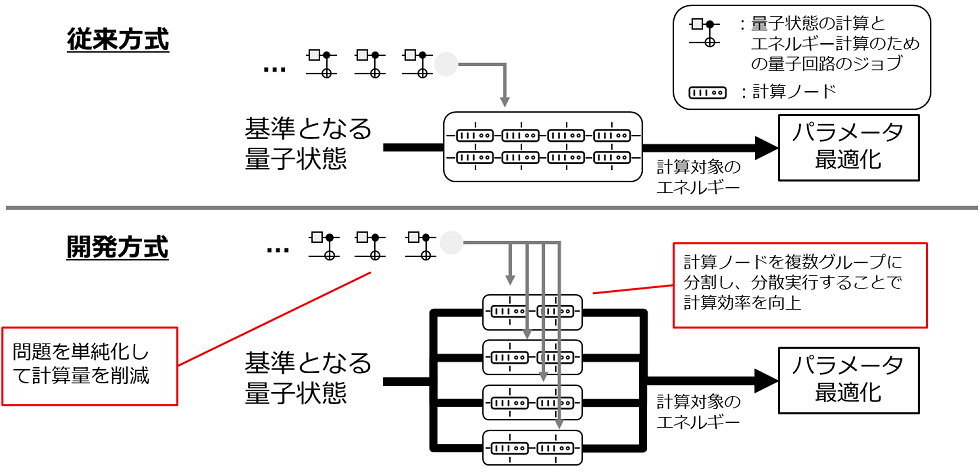

今回同社は、パラメーターを微小変更した量子回路それぞれが互いに影響を及ぼすことなく実行できることに着目し、量子シミュレーターの計算ノードを複数のグループに分割し、RPCの技術を活用しネットワークを通して量子回路計算のジョブを投入することで、各グループが異なる量子回路を実行できる分散処理を開発。これにより、計算時間を70分の1に短縮することが可能となった。

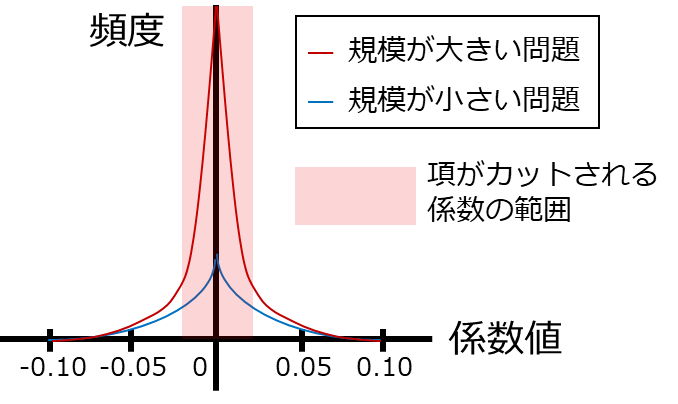

また、世界最大級という40量子ビットの量子シミュレーターの内32量子ビットを活用した規模の大きい分子のシミュレーションを通して、規模が大きくなるほど項の総数に対する係数の小さい項の割合が多くなること、かつ係数の小さい項が計算の最終結果に与える影響も微小であることを発見。この特性を利用し、式の項数の削減と計算精度の劣化防止を両立させることを実現し、量子回路計算時間をおよそ80%削減できたという。

これら2つの技術を組み合わせることで、32量子ビットの問題に対して1024の計算ノードを8つのグループに分割して分散処理した際、従来では200日と見積もられていた32量子ビットの量子シミュレーションの実行時間を、1日で実現可能なことを世界で初めて確認した。これにより量子ビット数の大きい問題に対する量子アルゴリズムの開発が進み、量子コンピューターの材料・金融の分野への応用が進むことが期待されるとしている。

今後、本技術を同社のハイブリット量子コンピューティングプラットフォーム「Fujitsu Hybrid Quantum Computing Platform」に搭載し、金融や創薬をはじめとする様々な分野での量子コンピューターの実用化を検討していくという。さらに本技術を応用して、量子シミュレーターのみならず、量子コンピューターでの量子回路計算を加速できることを検証する。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります