Arm、次々世代コア「Matterhorn」の機能を公表 機械学習向けに命令を追加

2019年10月10日 15時30分更新

Armは、米国で開催中のARM Techcon 2019で、次々世代のプロセッサとなるMatterhorn(マッターホルン)について,その機能の一部を公開した。

Matterhornは2021年に正式発表されるプロセッサか

機械学習を念頭に置いた命令を追加

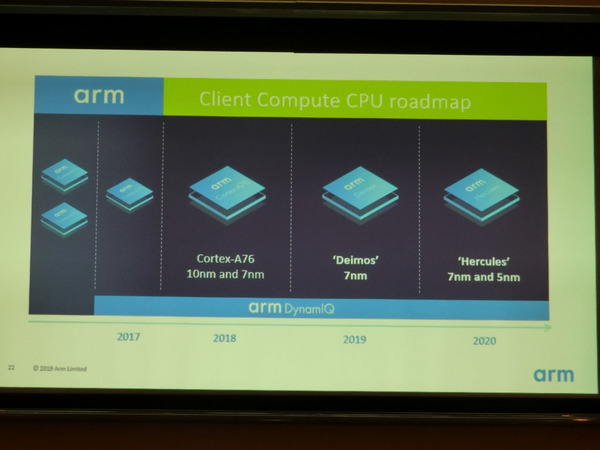

Armは昨年に、2020年までのプロセッサロードマップを発表している。

それによれば2019年はDeimos(今年発表のCortex-A77)、2020年がHercules(ハーキュリー、日本ではヘラクレスと読むことが多い?)となっていた。特に時期などを明示していないが、Matterhornは、Herculesの次、2021年に正式発表されるプロセッサだと思われる。

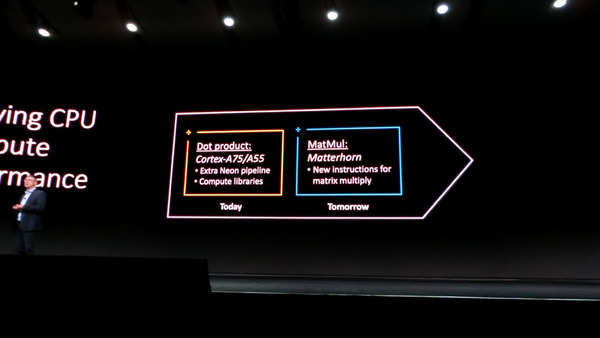

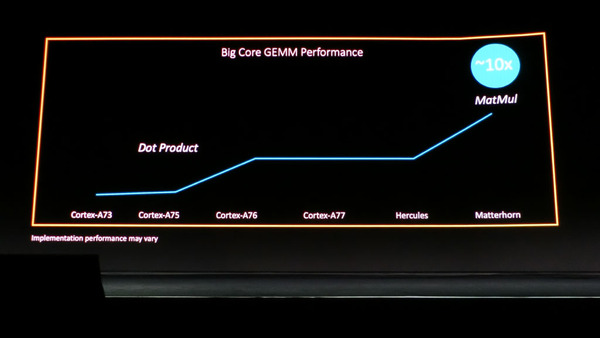

紹介された機能の1つは、行列演算機能だ。従来のNEON(ARMのSIMD演算機構)にも、内積を求めるSIMD演算命令はあったが、Matterhornの行列演算機能を使うと、Cortex-A77やHerculesの5倍、Cortex-A76の10倍の速度で演算が可能になるという。

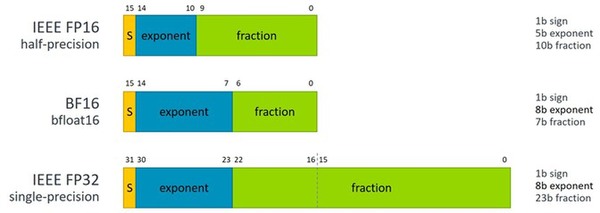

これは、2×4、4×2の行列の乗算と加算を1命令で同時に行い、2×2の行列を得るものだ。従来のNEONでは、ベクトル同士の内積計算しか行うことができず、2命令を必要としていた。また、データ形式として、BFloat16と呼ばれる形式をサポートする。BFloat16は、16bitで8ビットの指数部を持つもの。主にディープラーニングの学習時に使われるデータ形式だ。

Armは、これらのBFloat16や新しい命令群を“ML instructions”と総称する。複数の行列演算命令のほか、BFloat16と従来のFP32などとの形式変換命令などの命令が追加されるという。なお、Armのアーキテクチャでは、命令追加などが行われた場合には番号を変更する。最新のCortex-A77は、ARMv8.5である。ML Instructionsが加わることでアーキテクチャ番号は、ARMv8.6となる予定だ。

新しい行列演算命令やデータ形式への対応と“ML instructions”という名称などから、機械学習の学習処理をある程度念頭に置いたものと考えられる。このML Instructionは、サーバー向けのプロセッサであるZEUSなどでも採用することが2日目の基調講演で明らかにされた。

Armは、サーバー向け、クライアント向けに同一のアーキテクチャを採用している。このため、ARMv8.6を採用するMatterhornにも搭載されることになったようだ。メディア処理やAIなど、さまざまな「行列演算」の必要性は高まっており、学習処理をしないまでも、システム性能の向上が期待できる。

セキュリティを強化

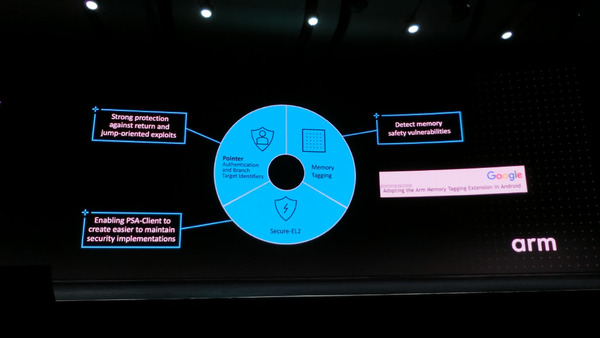

もう1つの強化点は、セキュリティ関連の機能だ。大きく3つある。

1つ目は、ブランチ命令の飛び先を認証されたアドレスのみに限る「Pointer Authentication」、もう1つはメモリ領域にタグを付け、正しいアクセスのみを許可するメモリタギング(Memory Tagging)機能である。3つ目は、Secure EL2だ。ELとはException Levelの略で、EL0~EL3の4段階ある。ELが高くなるほど、アクセスできるシステムレジスターや特権命令などの実行が可能になる。

通常アプリケーションはEL0で実行され、OSはEL1を使う。EL2、3は、ハイパーバイザーやセキュリティモニターなど、OSよりも高い特権で実行されるソフトウェア用だ。EL0/1/3には、セキュリティレベルの高いセキュアモードとそうでないノンセキュアーモードがあった。しかしEL2はノンセキュアーモードのみだった。Matterhornが対応するARMv8.6では、EL2でもセキュアーモードが利用できるようになるようだ。

Pointer AUthenticationは、簡単にいうと、ジャンプ命令の飛び先を認証されたアドレスのみに限定し、それ以外のアドレスへの飛び込みを禁止するもの。ジャンプ/ブランチ命令には、レジスタ内容を使った「間接」ジャンプ/ブランチがある。間接ジャンプは、レジスタ内容を書き換えてしまうことで、任意のアドレスに飛び込ませることが可能になるため、悪用されることが多い。

また、最近のOSでは、特定のソフトウェアモジュールが常に同じアドレスにならないように、メモリに読み込むときに乱数などで順番を変える機能がある。これをASLR(Address Space Layout Randomization)とよび、すでにAndroidなどでも採用されている。こうした機能に対抗するため、悪意のあるプログラムでは、レジスタ間接ジャンプ/ブランチを使うことが多くなってきた。

Pointer Authenticationは、間接ジャンプ/ブランチのレジスタ値を予め指定されたリストの中にあるアドレスに限定し、それ以外のアドレスのジャンプを禁止する。これをBranch Terget Indication(BTI)と呼ぶ。この機能により、間接ジャンプ/ブランチで任意のアドレスへ移行させる悪意のあるプログラムの動作を禁止できるほか、ソフトウェアのミスによる誤ったレジスタ値によるジャンプ/ブランチも検出可能になる。

Pointer Authenticationは、ARMv8.3で初めて搭載された機能だが、v8.3では、アドレスデータに対して認証データを付け、これをレジスタに読み込んでサブルーチンからのリターンなどを行う場合に正しいアドレスなのかどうかを認証していた。ARMv8.6では、こうした機能に加え、さらにBTIを追加した。

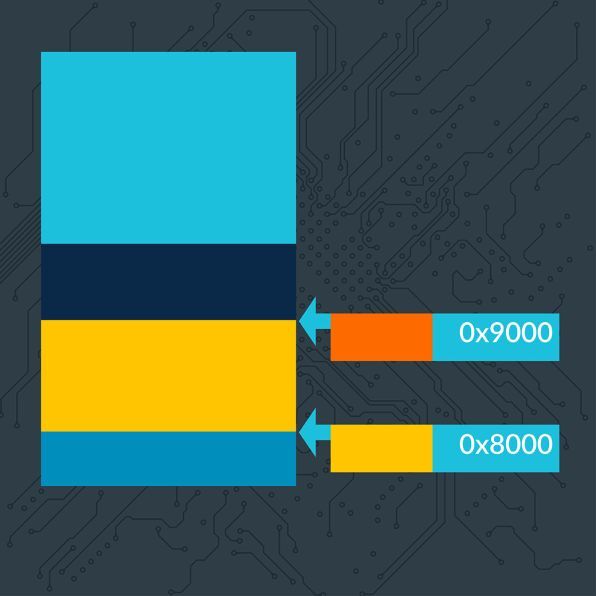

もう1つのメモリタギング機能は、MTE(Memory Tagging Extension)と呼ばれる機能。メモリ上のデータ領域やポインターを格納するレジスターにタグと呼ばれるデータを付ける。

そのために専用の命令が用意される。レジスタを使って、メモリをアクセスするときにCPUは、両者のタグを比較し、正しいタグの組合せのみを許し、それ以外はアクセス違反としてOSなどの処理に委ねる。プログラム開発時に、予定外の領域をアクセスしてしまうことなどを検出でき、また、悪意のあるプログラムなどからの不正アクセスも検出が可能だ。MTEは、Cortex-A77など、ARMv8.5を採用する一部のプロセッサに搭載されており、GoogleはAndroidでこれを検証し、有効性が確かめられたという。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります