既存半導体技術を用いて試作にも成功、次世代コンピューターとなるか

既存コンピューターの1万倍高速、実用性で量子コンピューターを凌ぐ新アーキテクチャ

2016年10月20日 17時51分更新

富士通研究所は10月20日、実用性において量子コンピューターを超えるコンピューターアーキテクチャを開発したと発表した。従来の半導体技術を用いつつ、量子コンピューターの得意とする組み合わせ最適化演算を高速で解くことができる。

組み合わせ最適化問題は、さまざまな組み合わせが存在するケースから最適な組を取り出す計算問題。チェスや将棋などのゲームはもちろん、実社会のほとんどの問題に存在する。最適解を得るためには多数の組み合わせを計算する分岐をひとつひとつ探索する必要があり、スーパーコンピューターを用いても計算に膨大な時間がかかってしまう。

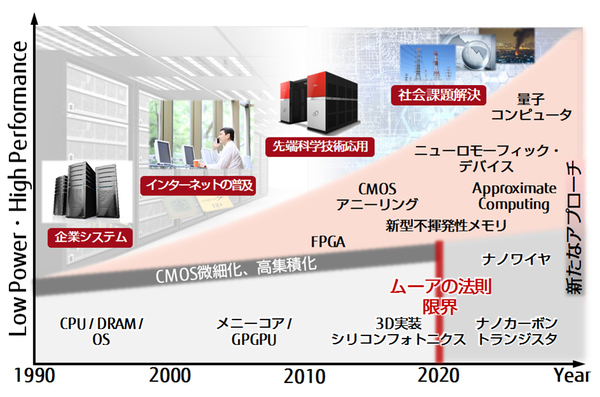

量子コンピューターが大きく期待されているのは、物理現象を用いることで最適な組み合わせをひとつひとつ計算することなく解にたどり着くことができ超高速に解が得られるという点。革新的なコンピューターであることは間違いないが、物理現象を用いるため近接した素子同士の接続しか扱えず、多種多様な実社会の問題に適用するのが難しいとされている。

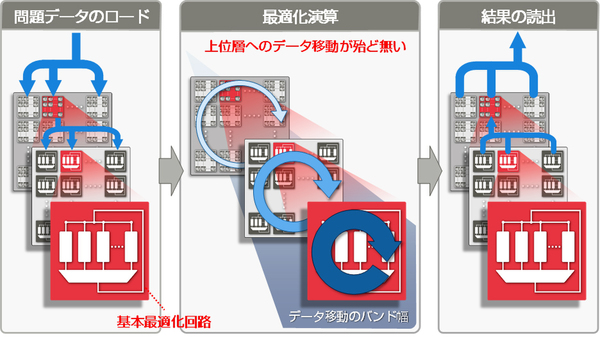

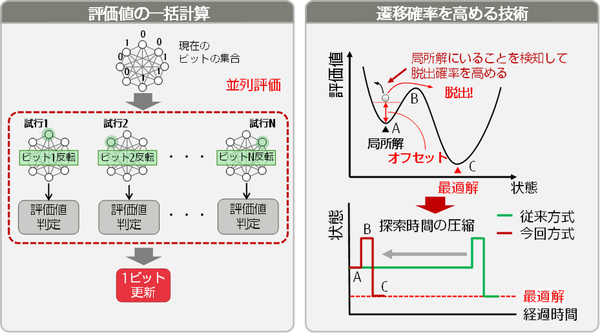

富士通研究所とトロント大学は、従来型の半導体技術を用いて組み合わせ最適化問題を高速で解くアーキテクチャの開発を試みた。デジタル回路を用いた基本最適化回路を1単位として複数単位を並列動作。回路は高密度で実装し、回路内外の信号のやりとりが行なえるようにしている。組み合わせ最適化問題を解く際には、複数ある状態の次の候補を探す際に各演算回路の評価結果を一括して並行計算する。

解を探索する途中で局所的な解にたどり着いて膠着状態になったときに検知して脱出する可能性を高める技術を導入しており、これが計算において分岐探索速度を高速化しているようだ。同社では、1024bitの組み合わせを扱うことができる基本最適化回路をFPGAに実装して評価。従来のプロセッサを用いた手法(シミュレーテッドアニーリング)に比べ、約1万倍という高速で最適解を得ることに成功したという。

富士通研究所では、開発したアーキテクチャーの改良を進め、2018年度までには実社会の問題が適用できる規模である10万bitから100万bitのシステムを試作し、実用化に向けて実証を進めるとしている。

週刊アスキーの最新情報を購読しよう

本記事はアフィリエイトプログラムによる収益を得ている場合があります